蘭NXP Semiconductorsは2月22日(現地時間)、英ARMより次世代ARMコア「Cortex-M4」のライセンスを受けた初めてのARM partnerになったことを明らかにした。Cortex-M4は2010年2月22日に英国にて発表された次世代コア。

ちなみにCortexシリーズは3種類に分けられ、それぞれ

- Cortex-A:アプリケーションプロセッサ向けに、高性能を追求

- Cortex-R:リアルタイムなど制御向けに、低レイテンシと高性能の両立

- Cortex-M:マイクロコントローラとして、低フットプリント/低消費電力を優先

といった分類がなされている。

実際Cortex-Aシリーズは当初登場したCortex-A8に続き、よりIPCを高めたCortex-A9や、やや性能を落とした普及帯向けのCortex-A5などのラインナップが用意され、特にSmartphoneやSmartbook向けに昨年末あたりから製品が登場しつつある。QualcommのSnapdragonやFreescaleのi.MX500シリーズ、NVIDIAのTegraの2世代目などにCortex-A8/A9が採用されているのはご存知の通りだ。

一方Cortex-Mシリーズもこれまた非常に普及しており、当初リリースされたCortex-M3はSTMicroelectronicsをはじめ主要なMCUベンダが相次いで採用を決めている。またこのCortex-M3のサブセットとしてFPGA上で動作するCortex-M1は、Actel/Altera/Xilinxの各FPGA上でソフトコアとして提供され、ライセンス料無しで利用することが可能だ。さらにローエンド向けにはCortex-M0も発表されており、こちらは16bit MCUと同等以下のフットプリントで動作するということで、NXPをはじめ何社かがライセンスを受けている。

比較的登場時期が早かったCortex-M3についてはSTMicroelectronicsやNXPなど、有力な16/32bit MCUコアをもっていなかったベンダが相次いで製品化したことで、今では8/16bit MCUのマーケットを脅かすほどの一大勢力になりつつある。

Cortex-M4は、こうした従来のCortex-Mシリーズの特長を引き継ぎ、組み込み市場におけるデジタル信号処理の効率や使い勝手の改善などCortex-M3の機能拡張版としての位置づけとなっている。

アーキテクチャはCortex-M3では「ARMv7-M」を用いていたが、Cortex-M4では「ARMv7-ME」へと変更されており、パイプラインの構造などに大きな変更はないものの(いずれも3-stage + branch speculation)、Single cycle 16,32-bit MACやSingle cycle dual 16-bit MAC、8,16-bit SIMD arithmetic、Hardware Divide (2-12 Cycles)に対応したDSPやIEEE 754(IEEE 浮動小数点数演算標準)準拠のFPUなどが追加された。

また、パイプライン構成などが同様であるため、処理性能も1.25DMIPS/MHzとCortex-M3と同等となっており、Interrupt Latencyは12cycles、Inter-Interrupt Latencyも6cyclesと同じだ。

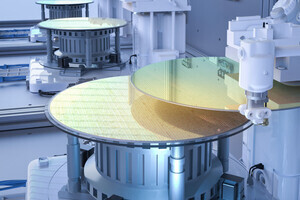

仮に65nm LPプロセスを用いて製造した場合、処理性能優先のStandard Cell Library「ARM SC12」を用いた時で、処理性能は375DMIPS、動作周波数は300MHz、電力効率は24DMIPS/mWとなり、シリコンの面積は0.21mm2となる。もし、FPUを追加する場合は、これにさらに0.08mm2の面積が追加されることとなる。

一方、シリコン面積優先のStandard Cell Library「ARM SC9」を用いた場合、シリコン面積は0.11mm2となりFPUを追加しても0.06mm2面積が増加するだけで済む。この場合の処理性能は150MHz駆動で185DMIPS、電力効率は38DMIPS/mWとなる。

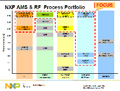

NXPはこのCortex-M4を、モータ制御/電力管理/組み込みオーディオ/産業機械制御といった、柔軟性と信号処理能力が必要とされる幅広い範囲の製品に応用してゆくとしている。