差動信号を使うクロック分配

図2.11のように分配されるクロックの波形が鈍ってしまうと、受端のバッファのスレッショルド電圧のバラつきによりSkewが生じてしまう。図2.12のように配線を太くしRCを減らすことで影響を減らすのは1つの手であるが、もう1つの手は、差動信号でクロックを伝送することである。

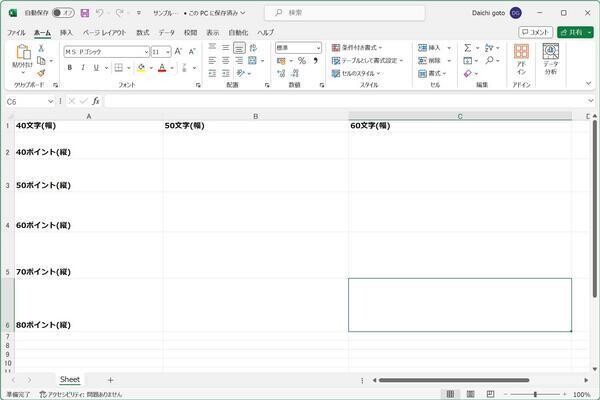

2本のクロック線を使い、図2.13のように互いに逆方向に変化するクロック信号を送り、差動型のクロックレシーバを使ってクロックを受け取ると、受信されるクロックのタイミングは両者の信号の電圧が同じになった時点になる。正確に言うと、差動のレシーバのスレッショルド電圧にも多少のずれが有るが、そのずれは単純なインバータのスレッショルド電圧のバラつきにくらべて非常に小さい値になる。

また、他の信号線から容量結合でクロック線にノイズが載っても、両方の線に同じようにノイズが載れば、それはキャンセルされてしまう。さらに、プロセサの電源電流は大きく変化するので、グランドや電源の電位は完全に一定ではなく、ここにもノイズが載っている。この電源ノイズもインバータのスレッショルド電圧をずらせる効果がありクロックのタイミングがバラつくが、差動レシーバは2つの信号間の電位だけに反応するので、電源ノイズの影響を受けず、タイミングのバラつきが少ないというメリットがある。

一方、差動伝送のコストは、単純に言うと2本のクロック配線とそれをドライブするバッファが必要となる点である。しかし、1本のクロック線を使う場合と比較すると、同じ精度であれば、立上り時間の長い信号で済むので、電力的には2倍よりも少なくなる。

クロック配線のシールド

配線の負荷容量のところで述べたように、配線容量の過半は隣の配線との間の容量である。従って、クロック分配を行うH-Treeの配線の隣の信号線の電位がスイッチすると、配線間の容量を通してクロックにもノイズが載る。これがクロックが変化するエッジの付近のタイミングで発生すると、両者の信号が重畳されてクロックエッジのタイミングがずれてしまう。また、この逆に隣接する信号配線に容量結合されたクロック信号が載り、エラーを引き起こすこともあり得る。

このため、図2.14に示すように、クロック配線の両側にグランドや電源といった電位の変化しない線を配置して、クロック線と信号線の容量結合を減らすという設計が取られる。このようにすると隣接配線の有無のよる配線容量の違いは発生しないので、負荷容量の均一性も改善できる。

また、両側にシールド線を配置すると、クロック線のリターン電流がシールド線を流れ、クロック線に鎖交する磁力線が減るので、クロック線のインダクタンスを低減するという効果もある。1mmのメタル8の配線は10GHzにおいては、シールド線が無く3μm下のグランドプレーンだけの場合は125+80jΩのインピーダンスであるが、両側にシールドを設けると137+37jΩとなり、インダクタンス成分は半分以下になる。

両側にグランド線を配置しても、クロック線と配線方向が直交する上下の層の配線との容量結合を除くことはできない。上下の層も同じ方向の配線としてクロック線の上下にもグランド線を配置すれば理想的であるが、これは配線設計全体に影響が大きく現実的ではない。

また、差動のクロック伝送の場合は、図2.15のように、両方のクロック線を隣接して配置し、その両側にグランド線を置く。このようにすると、クロック線は2本になるが、チップ上のスペースは2倍にはならない。

このようにクロックの+と-を隣接して配置すると、両方のクロック線への隣接する信号線からのノイズ電圧を近づけることができる。また、逆にクロック線からの容量結合や磁気結合による隣接する信号線へのノイズが+側と-側で相殺されて小さくなるという効果がある。