Hot Chips 28 - HPCへの進出を目論むARMのベクトル命令拡張(前編)はコチラ

次のコードは、倍精度浮動小数点計算でy[i]=A*x[i]+y[i]を求めるDAXPYという関数をスカラ計算(左)とSVE(右)で計算するものである。スカラコードの.loopから.latchの手前までが1回分のA*x[i]+y[i]を計算する部分で、SVEコードの場合はベクタの全要素を一括して処理している。そしてSVEコードではincd x4命令でループカウンタをVL/64増やして、ベクタ長分の要素を処理したことを反映している。そして、.latchのところのwhilelt命令で、まだ、処理する要素が残っているかどうかを判定し、残っている場合は、b.first命令で.loopに戻る。このような構造になっているので、このコードはハードウェアのベクタ長がいくつでも正しく動作する。

FFRレジスタを使うと、フォールトがあっても、そこまでのデータはベクトルとして処理することができる。次の図でZ3レジスタにA[0]~A[3]のアドレスが入っているべきところ、A[2]にはマッピングされていないアドレスが入っていたとする。

まずは、SETFFR命令でFFRレジスタのすべてのエントリをTrueにして、LDFF1D命令でロードを行うと、A[0]はFirst activeでロードが成功する。そしてA[1]はSpeculativeでロードが成功するが、A[2]のアクセスはSpeculativeで失敗する。しかし、このアクセスはSpeculativeなので、トラップは発生しない。そして、ハードウェアは、FFRレジスタのA[2]とそれより左のエントリをFalseに変更する。

2回目の繰り返しで、プレディケートのP1レジスタを再イニシャライズして、もう一度実行すると、A[2]のアクセスは今度はFirst Active状態で失敗するので、トラップが発生し、A[2]のアドレスにメモリを割り当てて処理を続けるか、あるいは、プログラムにバグがあるので処理を打ち切るかということになる。

このように、ARMのSVEでは、エラーがあるアドレスリストの場合でも、エラーの箇所を見つけるのが簡単であり、オンデマンドでメモリを割り当てて処理を続けたりすることができる。

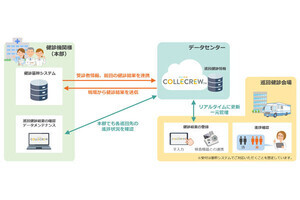

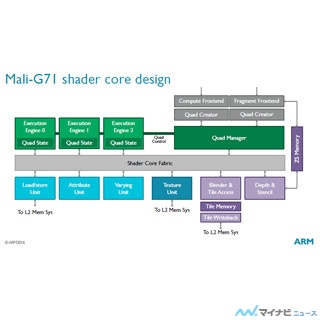

次の図は、各種のアプリケーションやベンチマークを実行した場合の、NEONに対するSVEの性能向上を示す図で、3本の折れ線は128bit、256bit、512bitのベクトル長のハードウェアの場合の性能向上を示している。棒グラフはベクトル化率の増加を示している。

この図から分かるのは、ベクトル化率が改善してない場合は、性能の向上も得られない。これは当然である。ベクトル化率が大きく改善している場合は、性能も向上し、右端のケースでは、128bitベクトルで3倍強、256bitベクトルで5倍強、512bitベクトルで7.3倍の性能向上が得られている。

しかし、全体として見ると、半分程度のアプリケーションで、NEONに比べて性能が向上していない。ハードウェアのベクトル長が4倍の512bitベクトルでも、4倍以上の性能向上が得られているアプリケーションは右端の3つだけであるというのは物足りない。今後のベクトル化コンパイラの成熟に期待したい。

|

|

SVEとNEONを比較したグラフで、棒グラフはベクトル化率の増加、3本の折れ線グラフは、128bit、256bit、512bitのSVEでの性能向上を示す。横軸は各種のアプリケーションやベンチマークで、性能向上が大きくなる順に並べている |

そして、次のステップとしては、SVEアーキテクチャを実装するパートナを増やすことと、コンパイラや開発ツールを開発してくれるオープンソースのコミュニティの支持を獲得して行くことをあげた。

現状では、NEONアーキテクチャは多くの実装で取り入れられている。128bitのベクトル長の実装であれば、SVE化しても演算器は増えないが、スキャッタ/ギャザーやプレディケートなどは追加のハードウェアが必要であり、多くのARMアーキテクチャのライセンシが付いてくるかどうかは未知数である。

富士通がポスト京での採用を表明

ARMのNigel Stephens氏に続いて、富士通のアドバンスシステム開発本部プロセッサ開発統括部第一開発部の吉田利雄氏が登壇して、富士通はARMv8-A SVEアーキテクチャに基づくHPC向けのプロセサを開発し、ポスト京コンピュータに使用すると発表した。

なお、Hot Chipsでの発表は、原則としてチップが完成していることが条件で、チップが完成していない場合でもテープアウトは終わっている必要がある。しかし、今のARMの発表は、チップは影も形も無く、富士通がポスト京向けに作るという決意表明が無ければ発表できたかどうか危ういのではないかと思われる。

|

|

富士通はARMv8-A SVEアーキテクチャのプロセサを開発し、ポスト京コンピュータに使用すると発表した吉田部長 |

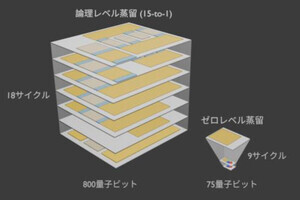

富士通は512bit長のベクタハードウェアを実装する。これは、現行のFX100システムと比較すると2倍の演算能力となる。この表に書かれたすべての項目は、FX100でも実装されているが、Post-Kでは、すべてがエンハンスされる。

そして、インタコネクトに関しては、京コンピュータで開発したToFuを使うが、Integratedと書かれているので、ネットワークインタフェースをCPUチップに内蔵するものと思われる。

富士通は40年以上のスパコン開発の経験があり、SPARC V9にHPC-ACEアーキテクチャを追加するなど、常に、最適なISAを作り上げてきた。今回は、ARMv8-Aアーキテクチャに対するスパコン向けのHPC拡張をARMと協力して開発してきた。

結果として、ポスト京コンピュータは、富士通の高信頼のHPCテクノロジを受け継ぐ、ARM ISAの超並列システムとなると述べた。