さて、以下個別に。まずFetch→Decodeの範囲であるが、これはCortec-A7にかなり近い構成に思える。ちなみにCortex-A7の場合、Decodeは完全2命令の同時Decodeが可能となっていたが、Cortex-A35ではこれがもう少し低くなっている可能性がある。実行段は極めて限定的なDual-Issueなので、実際には1.5命令/cycleまで行かないだろう。それを考えると、Decodeはもう少し動作速度を落として動かしても十分に思えるからだ。

もっとも2命令/cycleのままにして、Queueが一杯になったら停止する、というインプリメントとどちらが消費電力が少ないのかは微妙なところで、案外相変わらず2命令/cycleでDecodeが行われているのかもしれない。

またIssueが無いのは、Decode段に統合されているように思える。実際の所Queue→Decodeで2 Stageというよりは、Queue+Early Decodeで1 Stage、Late Decode(Issue含む)で1 Stageという感じだ。また分岐予測に関しては、さらに効率化を図ったとされている。具体的にはCortex-A35の改善点として、4KBのConditional Predictorと、256 entryのIndirect Predictorを搭載するとしている。Conditional PredictorはいわゆるBHT(Branch History Table)の事で、Indirect PredictorはBTAC(Branch Target Address Cache)ではないかと思うが、例えばBTACはCortex-A7だと8 entryだから、大幅にこれを強化した模様だ。もっとも、それでどの程度Efficiencyが向上したのかは今の所公開されていない。Load/Storeに関しては、遂に自動Prefetchが搭載されるようになった。ただこれはあくまでもアドレスベースの、それも簡単なものに留まっており、あまり複雑な事はやってないとの事。このあたりは性能とダイエリア&消費電力のバランスなので、あれこれ搭載すればいいというものでもないのだろう。

ちなみに説明の中にはInteger ALUに関するものは割愛されているが、これはおおむねCortex-A7と変わらないと思われる。もちろん64bit命令をサポートするから、Cortex-A7そのままでは済まないと思うが。恐らくExecuteが2 stageで、それにWritebackが入ってトータル3 stageと思われる。あとこのスライドには入っていないが、512 entryのMain TLBとは別に、10 entryのμTLBが別に用意されており、こちらを利用できる場合にはLatencyがかなり減るとされている。

|

|

|

Photo07:この図だとDecodeの前にInstruction Queueがあるように描かれているが、実際はCortex-A7のようにDecode済の命令を格納する形と思える |

Photo08:Automatic Write stream detectionも、いわゆるx86系プロセッサで言うところのWrite-combinationのようなものではないとの事 |

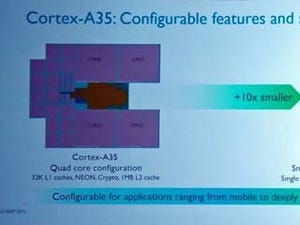

L2回り(Photo09)に関しては、基本効率を改善したということしか明らかにされていない。ただL2のサイズは128KB~1MBとされており、Cortex-A53が最大2MBを搭載できるあたりと比べると、より低い性能レンジに合わせた構成になっていることは間違い無い。Cortex-A7がやはり最大1MBというあたりからもこれは明白である。

|

|

Photo09:こちらにもあるようにL2は必須ではない |

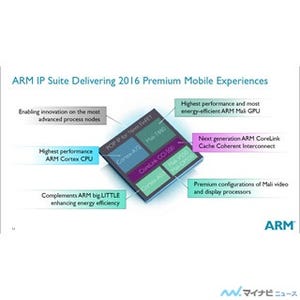

Cortex-A7と比べると大きく性能が改善されたのが、FPU/NEONである(Photo10)。ここにもあるように、単精度で2倍、倍精度で5倍のスループットが実現されているとする。バスI/FはAXI4/AMBA4 ACE/AMBA5 CHIが搭載されており、必要ならACPがさらに利用できる(Photo11)。最後がGovernor(ガバナー)である(Photo12)。これだけ見ると何をやっているのか良く判らないかもしれないが、これは省電力のところで説明したい。

|

|

|

|

Photo10:普通に考えればNEONの実装がCortex-A15などと同じように128bit幅に拡張されたものと思われる。Cortex-A7はCortex-A8/9と同じく64bit幅だったので、これで倍増である。ちなみに倍精度に関してはNEONではサポートされないので、これはFPU側の問題である |

Photo11:流石にAMBA5 AHBはここにはあがっていない。ただAMBA5 AHBは既存のCortex-Aと互換があるということなので、接続には問題は無いのだろうが(これは次のARMv8-Mの記事で説明したい)。ちなみにAMBA5 AHBのプロトコルは11月24日に公開されている |

Photo12:こちらはGovernor。これについては、後ほど詳しく説明したい |

次がいくつか性能に関するもの。まずPhoto13は見ての通りで、同じプロセス/動作周波数で32bitのアプリケーションを稼動させた場合でも16%ほど高速であり、また同じ28nmでも速度よりに振ると2GHzまで性能が上げられ、その場合84%高速になるとする。

|

|

Photo13:Browsingということなので、Androidの上でBrowser Performanceの比較を行っていると思われる。グラフで左の2つは28nmのLPあたり、右はHPあるいはHPMあたりを利用したケースであろう |

とりあえず動作周波数が違うと比較が難しいので、同一周波数上で性能比較を行ったのがこちら(Photo14)。基調講演で出てきた6~40%の性能改善はこれを基にしたと思われる。

|

|

Photo14:GeekBenchについては「言いたいことは判ってるから言うな。我々は色んなベンチマークを並べて少しでも客観的な比較を出したいのであって、そのうちの1つがこれだったんだ」(Ian Smythe氏)。今年4月のARM Tech Dayでボロクソに叩かれたのが余程懲りたらしい |

またL1/L2の性能改善により、メモリアクセスの性能を大幅に改善したとしており(Photo15)、これも全体としての性能改善に寄与している。また暗号化アクセラレータを搭載したことで、セキュリティ関連が大幅に高速化された(Photo16)。

|

|

|

Photo15:もっともこれは改善しないと折角NEONの性能を強化したのが無駄になるので、必然ではある |

Photo16:これはこちらにも出てきたCryptoCell-700の話ではないかと思うのだが、うっかりして確認するのを忘れてしまった |