多出力のクロックジェネレータによってシステムクロック回路を簡素化する方法について説明します。この方法により、複数のシステムクロック信号を供給可能なクロックサブシステムを設計する際の課題に対処することができます。

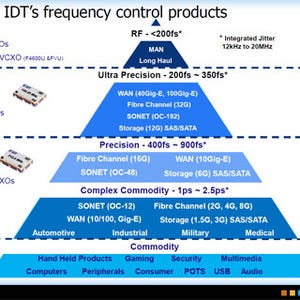

システムの複雑化はとどまることがありません。最新のシステムでは、多くの場合、その基板に特定用途向けのプロセッサ、高性能の汎用プロセッサ、複数のSoC(System on Chip)を搭載しています。そうした高性能のICは、必ずしも互いに連動することを前提として設計されているわけではありません。そのため、それぞれにクロック周波数に関する要件が異なります。また、基板上の各ICでは、クロックの安定性(ジッター)やクロックのデューティサイクルといったタイミング面で異なる制約があるでしょう。このような理由から、複雑な基板を設計する際には1つの重要な課題が浮上します。それは、各IC(回路ブロック)に複数のシステムクロック信号を供給し、多数のサブシステムのタイミングを管理することが可能なクロックサブシステムを設計しなければならないということです(図1)。セットトップボックス/DVR、ハイエンドのデジタルテレビ、ネットワーク用のスイッチ/ルータ、データサーバといった多くの用途で、そのような基板を設計する必要が生じます。

|

|

|

図1:一般的なセットトップ・ボックスのブロック図。クロックの周波数や安定性に関する要件がそれぞれに異なるさまざまな回路ブロックを搭載している。何種類ものタイミング信号を供給するために、通常は複数のクロック発振器が使用される |

ここで問題になるのは、複数のクロックの同期をとって最大のタイミングマージンが得られるようにするためには、複数のクロックをプログラムに出力可能な低ジッターのクロック源が必要になることです。基板上に複数の独立した水晶発振器を配置していたのでは、十分な信頼性を得ることはできません。それらの同期をとるのは簡単ではないからです。また、1つの基板に水晶振動子とCMOSの水晶発振器を5つも6つも搭載すると、製造コストがかさみます。さらには、EMI(電磁干渉)を抑制するためのスペクトル拡散機能もそのままでは利用できません。

このような理由から、同期をとったクロック信号を基板上のさまざまなサブシステムに供給するための最良な手法が見えてきます。それは、PLLによって制御された複数の出力を備える集積度の高いクロック源を使用することです。この方法を使えば、基板面積を削減できるとともに、設計の複雑さも緩和されます。また、システムコストを低減できる可能性もあります。今日では、信号品質を損なうことなく、回路基板上の長い配線経路に対応できるクロック信号が求められています。配線経路が長いと、スイッチングノイズが生じたり、容量性の負荷によって信号が劣化したりことがあります。加えて、プリント回路基板上の配線が異常に長い場合には遅延も問題になります。

セットトップボックスなどの一般的なシステムは、さまざまなサブシステム(機能ブロック)から構成されます。通常、各サブシステムは、それぞれが実現すべきシステム機能に応じて異なる周波数で動作します。PCIやPCI Expressなどのインタフェースは、求められるデータ転送速度に対応して単一の周波数(基本周波数の整数倍)で動作します。USBインタフェースも同様ですが、イーサネットの場合、データ転送速度に依存する複数の周波数要件があります。ビデオ信号などを扱う追加機能や、メインのASIC/プロセッサにも、クロックに関してそれぞれ固有の要件があります。

どのような用途を対象とするシステムであっても、すべての設計者にとってジッターは共通の問題です。ジッターは、回路基板上で分配される複数のクロック信号のタイミング・マージンに悪影響を及ぼす恐れがあるからです。また、データの転送速度とシステムのクロック速度が高まり続ける中、タイミング・ジッターはシステム設計における重要な要素となっています。多くの場合、システムの性能はシステムのタイミング・マージンからの制約を受けます。したがって、システムを設計するに当たっては、タイミング・ジッターについて十分に理解しておくことが非常に重要になります。

トータル・ジッターは、ランダム・ジッターと確定的ジッターから成ります。クロックのタイミング・ジッターは、時間領域と周波数領域の両方で測定されます。周期ジッター、サイクル間ジッター、TIE(Time Interval Error)ジッターは時間領域で測定し、位相ノイズと位相ジッターは周波数領域で測定します。ジッターの原因としては、熱雑音、電源ノイズ、クロストーク、信号の反射などが挙げられます。