研究で見えてきたプロセサにおける消費電力の低減手法

4月16日に開催されたノーマリーオフコンピューティング基盤技術開発プロジェクト(Noffプロジェクト)の公開シンポジウムにおいて、東芝の藤田忍氏がプロジェクトの成果報告を発表した。

Noffプロジェクトは新エネルギー・産業技術総合開発機構(NEDO)が開発費の一部を負担するプロジェクトで、東大の中村宏教授がプロジェクトリーダーとして研究開発を率い、東芝、ルネサス、ロームが企業として参加している。

このプロジェクトに東芝はNoffの携帯情報端末の開発担当として参加し、高速低消費電力のSTT-MRAMの開発と、そのSTT-MRAMをキャッシュに使用して消費電力を低減するプロセサの開発を行っている。その中間成果を今回の公開シンポジウムで発表した。

現状、スマートフォンやタブレットなどの携帯情報端末では、ディスプレイ、無線などのプロセサ以外のチップセット、プロセサがほぼ1/3ずつの電力を消費している。しかし、ディスプレイやチップセットの消費電力は減る傾向にあるのに対して、プロセサの電力は高性能化によるアクティブ電力の増加、キャッシュの増大によるリーク電流の増大により、むしろ増加すると見られている。このため、近未来を見ると、プロセサの消費電力の低減が重要になるという。

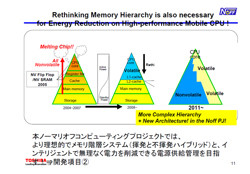

不揮発メモリの動作エネルギーはフリップフロップ(FF)やSRAMよりも大きいので、単純にプロセサ内部のFFやSRAMを不揮発メモリに置き換えると、動作時の消費電力が大きく増加してしまう。このため、動作頻度が高いプロセサコア内部のレジスタや1次キャッシュは動作エネルギーの小さいFFやSRAMを使い、動作頻度が少なく量の多いL2キャッシュ以下はアイドル時には電源をオフしてリーク電流を抑える。ここでL2キャッシュ以下は不揮発メモリを使うと電源をオフしてもデータを保持できるので、動作を再開する場合のデータの再読み込みを不要にして復帰時間の短縮とエネルギー消費を減少させるというのが一般的な不揮発メモリの使い方である。

しかし、これまでのNoffプロジェクトの研究で、下図の一番右のピラミッドのように、各階層で適材適所で揮発性と不揮発性のメモリを混在させるのがベストであることが分かったという。

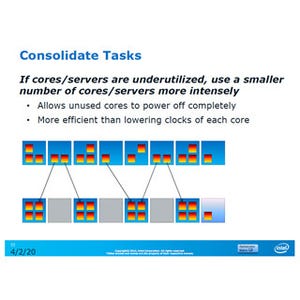

次の図は、電源をオフできる機会の累積出現頻度とオフ期間の長さの関係を示すグラフで、ミリ秒単位でオフできる機会は少ないがマイクロ秒単位、さらにナノ秒単位と期間が短くなるにつれてオフできる機会の出現頻度は増えていく。

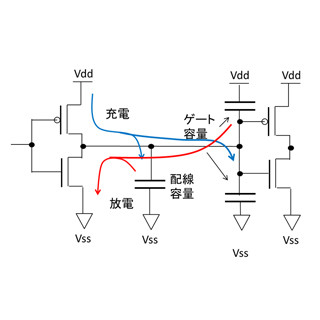

より短いオフ期間にも対応できれば、リーク電力を減らせるが、電源のオンオフに伴うオーバヘッドの電力が増えるというジレンマがある。このオーバヘッドを小さくすれば、時間的により細粒度のパワーゲートができ、消費電力を減らせる。このため、数10ns程度のオフの機会も有効に利用できる構造の実現を目指すという。

なお、ミリ秒以上のオフ期間であればOSの制御で間に合うが、それより短くなるとハードウェアのIPブロックレベル、さらに数十nsになると回路レベルでパワーゲートを行うことが必要になる。