Linuxをサポートしたx86コプロセサ「Xeon Phi」

Hot Chips 24でIntelは、 MIC(Many Integrated Core)の「Xeon Phi」というブランドの最初のチップについて発表を行った。このチップはKnights Cornerのコードネームで開発されてきたものである。

|

|

|

Hot Chips 24においてIntelはメニーコアXeon Phiの最初のチップであるKnights Cornerについて発表した |

Knights Cornerについ発表するGeorge Chrysos氏 |

このチップはIntelのx86アーキテクチャをベースに512ビット長のSIMDベクトルユニットを追加したコアを50個以上搭載するもので、Intelはコプロセサと位置付けている。その点ではNVIDIAのTeslaシリーズの科学技術計算向けGPUと同じであるが、Knights CornerはLinux OSをサポートできると発表された。Linuxを走らせるためには、メモリ管理機構や割り込みの処理などが必要であるが、Knights Cornerはこれらの機能をサポートしているということを意味する。また、汎用のXeonプロセサとKnights Cornerの間のインタフェースはx16のPCI Express Gen3.0(PCIe 3.0)となっており、PCIデバイスとして動作させる以外に、Xeon CPUからTCP/IPで繋がっているように使うこともできるという。

そして、Knights Cornerは8GB以上のGDDR5メモリを接続と書かれており、メモリもGPUと同じような構成である。

そして、2012年6月のGreen 500のデータをもとにKnights Cornerは電力効率が高いことをアピールしたが、具体的な演算性能や消費電力は発表されず、これらは、2012年第4四半期と予想される製品発表まで待たなければならない。

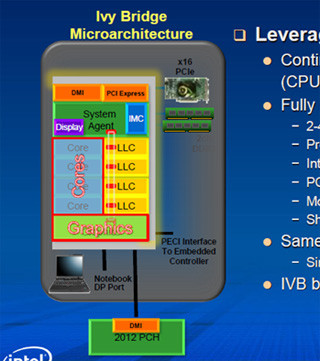

このKnights Cornerのマイクロアーキテクチャとして、次の図が示された。

Knights Cornerでは、コアとL2キャッシュのスライスがペアになっており、これが50ペア以上存在し、それらをリングで接続している。そして、それぞれのL2キャッシュスライスに対応するTD(Tag Directory)もリングにつながっている。

左側の図では、4個のGDDR MACとPCIe Client Logicと書かれたブロックがリングにつながっている。この図ではGDDR MACはリングの左右の辺に2個ずつあるが、右の図では8個のGDDR MACが描かれており、4辺に2個ずつのGDDR MACが付いている。会場では、この違いに関して質問が出たが、これらの図は概要を示すもので、詳細な構成を示すものではないという回答であった。

Knights Cornerのコアに関しては、より詳細なブロック図が示された。

各コアは2命令を並列にデコードするIn-Orderコアで、4スレッドのマルチスレッドをサポートしている。並列にデコードする2命令の内の一方はPipe0で処理し、もう一方の命令はPipe1で処理する。Pipe0は512ビット幅でSIMD演算を行うVPU命令を含めてすべての演算ユニットに対する命令を扱えるが、Pipe1はスカラ演算の処理だけに限定されている。そして、各コアは32KBの1次命令キャッシュ、32KBの1次データキャッシュと512KBの2次キャッシュを持ち、2次キャッシュからリングにつながっている。

この図に見られるようにx87 FPUなど盲腸のようなレガシーの機能も残っているが、x86アーキテクチャを実現するために必要となる論理回路は全体の面積の2%以下であり、x86を実現するためのオーバヘッドは大きくないとのことである。