Hot Chips 24においてIntelのSanjeev Jahagirdar氏が、第3世代CoreアーキテクチャのIvy Bridgeの電力制御技術を発表した。

良く知られているように、IntelはTick-Tock(日本語ではチクタク)と呼ぶプロセサの開発戦略を取っている。Tockでは、マイクロアーキテクチャを大幅に改良して性能や機能を上げる一方、半導体プロセスは前世代と同じ安定したものを使う。一方、Tickでは新しい半導体テクノロジを使って性能を向上したりチップサイズを小さくしたりするが、アーキテクチャ的には前世代のマイナーチェンジで済ます。新しいアーキテクチャや新しい半導体プロセスの開発には相当なリスクが伴うが、Tick-Tockにすると両方のリスクを一度に背負い込むことが無く、かつ、毎年、性能や機能を改善した新製品を出すことができるというメリットがある。

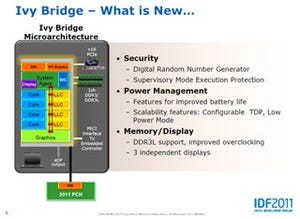

Ivy Bridgeは2012年4月23日に発売を開始した第3世代のCoreアーキテクチャのプロセサであり、開発戦略上はTick世代にあたる。ということで、主要な改良はTriGateと呼ぶ3次元トランジスタを使う22nm半導体プロセスを使った点である。

|

|

Ivy BridgeはIntelの22nmプロセスを使う最初のコア製品。(なお、Hot Chips 2012と書かれているスライドはすべてHot Chips24でのIntelの発表資料より抜粋したもの) |

2~4個のIAアーキテクチャのプロセサコアとグラフィックスやメディアエンジン、メモリコントローラ、PCI Expressコントローラなどを搭載し、主要な高速IOはこのCPUチップに直結できる。そして、その他の比較的低速のIOはDMIを経由してPCHと呼ばれるチップを接続してサポートされる。

しかし、前世代のSandy Bridgeを22nmプロセスで縮小しただけではなく、グラフィックスエンジンは大幅に強化されているし、16bitの短い浮動小数点演算のサポートや物理乱数発生などのセキュリティ機能の強化も行われ、IPC(1クロックあたり実行できる平均命令数)の向上などが行われているのであるが、なかでも注目されるのが、今回発表された省電力技術である。

細かいところまで手が入ったIvy Bridgeの消費電力低減技術

Ivy Bridgeの電源系は、プロセサコア、最終キャッシュ(Last Level Cache:LLC)、システムエージェント/ディスプレイ、グラフィックス、その他の5種類に分かれており、それぞれ、独立に電源電圧を設定することができる。そして、各コアには電源スイッチが付いており、必要なプロセサコアだけに電源を供給し、その他のコアは電源オフとすることができる。また、PCI Expressのコントローラも電源スイッチがあり、そのポートに何も接続されていない場合は電源オフとしている。DDRメモリはセルフリフレッシュ状態の場合はプロセサから信号を送る必要がないので、動作を止めて電力を節約している。

半導体のPN接合に電流が流れると、そのごく一部のエネルギーが赤外線となって放出される。シリコンは可視光では不透明であるが、赤外線では透明なので、チップの裏側を赤外線顕微鏡で見ると、トランジスタが動作している部分が明るく見える。次の図は赤外線観測を行い、赤から白、青の疑似カラーで動作状態を示したものである。

|

|

左は1コアがターボ状態で残る3コアは電源オフの状態、中央は通常の状態で、4コアと下側のグラフィックが動作している状態、右はコアとグラフィックはパワーオフの状態で、キャッシュだけわずかに電力を消費している状態 |

このようにして見ると、パワーゲートで電源をオフにした効果が良くわかる。なお、右側の図でキャッシュのSRAM以外に明るい点がポツポツと見られるが、これらはクロックの分配系などの高速の動作が続いている部分である。

最近のプロセサでは、高性能を必要とする場合は電源電圧を上げてクロックを上げ、仕事が無い場合には逆に電源電圧とクロックを下げて電力を減らすDVFS(Dynamic Voltage Frequency Scaling)という手法を使うものが多く、Sandy BridgeやIvy Bridgeもこの手法を使って省電力化を行っている。

ある周波数で動作させるために最低限必要な電源電圧は右上がりのなだらかな曲線になるが、Sandy Bridgeでは、定格のクロック周波数と最低、最高周波数の3点での最低動作電圧を測定して求め、中間の周波数での動作電圧は図の青線のような折れ線で近似していた。これは動作上は十分であるが、中間周波数では本当に必要な電圧より若干高い電圧で動作させることになっていた。これをIvy Bridgeでは赤線のように2次曲線に変更し、中間の周波数で動作させる場合の電源電圧を引き下げた。

これで下げられる電源電圧は最大でも数10mVと考えられ、消費電力の削減はそれほど大きなものではないが、乾いたタオルをさらに絞る努力である。

SRAMメモリセルは、すべてのトランジスタがバラつきなく作られている場合は良いが、トランジスタの製造バラつきがあると、0を記憶しやすいとか1を記憶しやすいというような偏りが生じる。この偏りのため、読み出し時に記憶しやすい方の値に化けてしまう、あるいは、記憶しやすい方と逆の情報が書き込めないということが起こる。この問題は電源電圧を下げるにつれて小さな偏りでも発生するようになり、SRAMがどれだけ低い電源電圧で動作するかを決めている。

Ivy Bridgeの最終レベルキャッシュ(LLC)は8MBあり、16個のWayと呼ぶサブブロックからなっている。処理する仕事が一杯ある時には、全部のWayを使うが、仕事が少なくヒマな時には2つのWayだけを使い、その他のWayはクロックを止めてスリープさせてしまう。

各Wayの512KBのSRAMの中で最も高い電圧でないと動作しないセルが、そのWayの最低動作電圧Vminを決めるが、SRAMのトランジスタのバラつきはランダムなので、使用するWay数を減らせば、最悪のWayを外れる可能性が高く、2Way動作の場合は平均的には30mV低いVminで動作させることができるという。そして、LLC部の電源電圧を30mV下げた分、電力を削減できる。

この削減も、チップ全体の電力からいうと1%になるかどうかという程度と思われるが、Intelの乾いたタオルをさらに絞る努力である。

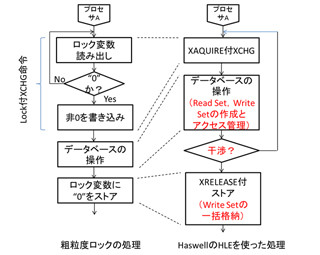

各コアへの通知を状態に応じて判断することでも電力を削減

通信インタフェースにパケットが届いたとか、ディスクコントローラがコマンドで指示された動作を完了したとかの事象は割り込み(Interrupt)で通知される。従来は、この割り込みがどのプロセサコアに通知されるかは決まっていた。しかし、電源がオフのコアに割り込みを通知してしまうと、そのコアは電源をオンにして動き始める必要があり、割り込みへの応答時間が長くかかってしまう。また、電源オフのコアを起こすにはエネルギーを必要とするという問題がある。

一方、1つのコアに割り込み処理が集中してしまうとそのコアが過負荷になってしまうので、寝ているコアを起こす方が良いという場合もある。例えば、1コアがフル動作のC0ステートで、1コアが電源オフのC6ステートの場合、電力的にはC0ステートのコアに割り込みを通知するのが良いが、負荷分散の点からはC6ステートのコアを起こす方が良い。

そのため、コアの状態を示すC-Stateとターボかノンターボかなどの状態から、どのような処理がベストかを決めるという。Intelは、この機能を「PAIR(Power Aware Interrupt Routing)」と呼んでいる。

これらの努力の結果、Ivy BridgeではSandy Bridgeに比べて平均的に10%~20%パワーを減らすことが出来たという。ただし、これはサンプルチップでの測定で、製品ではこの値は異なるかも知れないという注意書きが付いている。

なお、この結果はMobilemark 07とBlue Ray Playbackだけの測定であり、後者の測定での削減が多いという結果になっている。Blue Ray PlaybackはCPUの使用率の低いアプリケーションで、Mobilemarkの結果に注目すると、モバイルの平均的な使用状態での電力削減は10%かそれ以下という見方もできる。とは言え、大きな電力削減が可能な手段はすでに実装されており、乾いたタオルを絞る地道な努力による省電力化の積み重ねが重要になってきている。