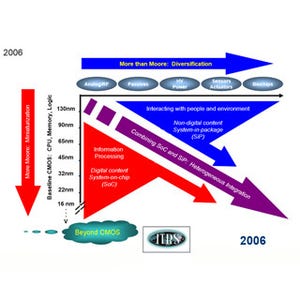

微細化が限界に近づき、ムーアの法則が終わりつつある状況であるので、ムーア以降の時代をどのように乗り切っていくのかは大きな問題である。このムーア以降の時代をどうするのかを検討するのが、「リブート・コンピューティング(正式名称はRebooting Computing Initiative:RCI)」である。IEEEは2013年末にIEEE Rebooting Computingの第1回会合を開いている。

一方、半導体の業界団体(Semiconductor Industry Association:SIA)は半導体のロードマップを検討する活動を行っており、International Technology Roadmap for Semiconductors(ITRS)というロードマップを発行してきた。

しかし、微細化だけで半導体やコンピューティングの進歩を考えることができなくなっており、ITRSの検討は2015年を最後とし、ロードマップの作成は、IEEEの規格委員会が担当することになった。IEEEには半導体からコンピュータまで多くの専門家が揃っており、半導体デバイスだけでなく、コンピュータアーキテクチャや情報処理の方式まで、より広い視野でコンピューティングのロードマップを検討することができる。

そして、より広い視野で検討を行うことから、新しいロードマップは、「International Roadmap for Devices and Systems(IRDS)」と呼ぶことになった。なお、IRDSの検討はIEEEに移ったのであるが、ITRSを担当していた多くのメンバは引き続き、IRDSの検討に参加するという。

このRCIとIRDSについて、IEEE RCIの共同議長とIRDSの副議長を務めるジョージア工科大学のTom Conte教授が、SC16のワークショップで発表を行った。

|

|

|

SC16のワークショップでRCIとIRDSについて発表するTom Conte教授 |

コンピューティングを根本から見直すRCI

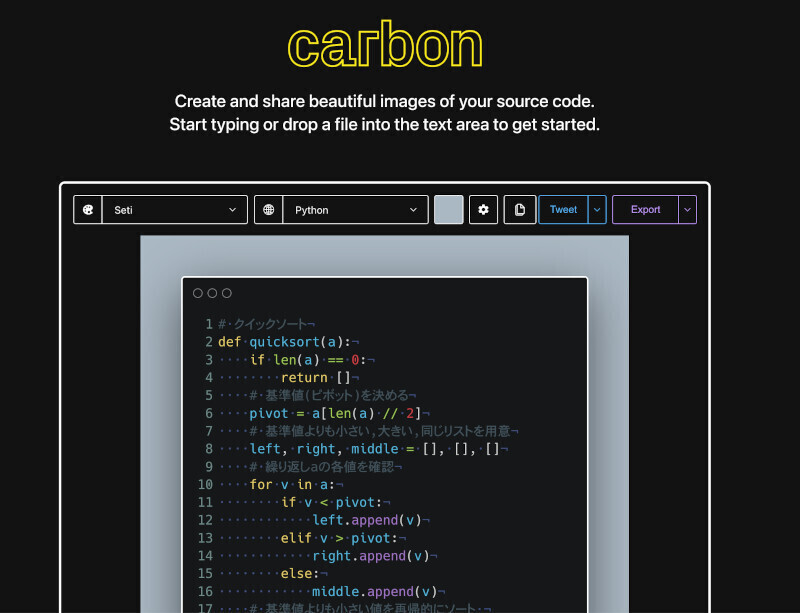

これまで、2次元の微細化がコンピュータの発展を支えてきたが、微細化は終わりに近づき、まだ、ある程度の微細化はできるものの、トラジスタの動作速度はほとんど向上しないという状況になっている。この状態で、さらにコンピューティングの発展を実現するためには、コンピューティングを根本から見直すリブートが必要であるという。

|

|

|

|

リブートは、チューリングやフォンノイマンから現在に至るコンピューティングすべてを考え直す (このレポートのすべての図は、Conte教授の発表スライドを撮影したものである) |

RCIの2014年10月の3回目のサミットで、ITRSがRCIに加わることとなった。 |

デバイスだけを変えるLevel1、変更がマイクロアーキテクチャレベルに留まるLevel2、命令レベルに変更が起こるLevel3、非ノイマンコンピューティングまで考えるLevel4が考えられる。Levelが上がると性能向上(Gain)の可能性が増えるが、それに合わせてソフトウェアを作る手間(Pain)が増えるというトレードオフになる。

Level1はMore Mooreで、レガシーのコードがそのまま動く。トンネルFETやCNFET、超電導素子などのよりよいロジックスイッチや、MRAM、メモリスタ、PCMなどのより良いメモリを探すというアプローチである。

|

|

|

|

Level1はMore Mooreで、レガシーのコードがそのまま動く。トンネルFETや超電導素子などのよりよいスイッチを探す |

Level2はレガシーコードは一応動くが、最適化は違ってくる。マイクロアーキテクチャとしては、信頼性の低いスイッチを使う、超電導ロジックを使う、可逆的コンピューティングを使うなどが候補である |

トランジスタ回路の電源電圧を下げると、2乗に比例して消費電力が減少する。しかし、電源電圧を1V以下に下げると、熱雑音による信号レベルのふらつきが無視できなくなる。結果として、確率的にスイッチの誤りが起こる。

しかし、このようなスイッチでも、3重化して多数決を使ったり、冗長付きのモジュロ数を使うことで誤りを訂正すれば、使うことができる。3重化は200%のオーバヘッドであるが、冗長付きモジュロ数を使うと50%のオーバヘッドで済む。

超電導素子は、超低温で動作させるので熱雑音(kT)が小さく、低い電圧でも安定に動作させられるので、動作電力が非常に小さく、高速で動作するというメリットがある。

しかし、この図にも1cm2に1万アンペアの電源供給と書かれており、筆者には、数mVで1万アンペアなどというDC電源が効率よく作れるとは思えない。冷却電力を含めて本当に得かどうかはちゃんと評価する必要があると思われる。

CMOS以外の素子で、Exascaleのコンピュータをけた違いに低い電力で実現できる可能性はあるが、かなり多額の研究開発費が必要になることは間違いない。

レベル3はアーキテクチャを変えて高性能を実現しようというアプローチで、ソフトは、そのままでは使えない。GPUはこの一例で安価な並列性を提供しているが、プログラムは新たに作る必要がある。また、HPEのThe Machineのようにメモリセントリックなコンピューティングもこの範疇のアプローチである。

アクセラレータは、1961年のIBMのStretch以来の高性能化手段である。並列化で性能を上げ、命令のフェッチやデコードを省略して消費エネルギーを節約する。ソフトウェアの変更が必要であるが、コンパイラにやらせる、ドメインスペシフィックな言語を使うなど、ソフトの変更の手間を減らす手はある。

近似値コンピューティングは、出力の精度を犠牲にして、効率や性能をあげるアプローチである。信頼度/精度の低いハードウェアやソフトウェアから許容できる信頼度のシステムを作る。

人間が見るイメージやビデオの場合、それほど高い精度は必要ない場合が多い。あるいは、サーチの場合、最適な場合を見つけられなくても、最適値に近い場合を見つければよいというケースも多い。

ただし、出力に必要とされる精度を保証するためには、どのようなアルゴリズムを使えば良いかは、まだ、分かっていない。

Level4は非ノイマン型のアーキテクチャで、量子コンピューティング、アナログの神経回路によるコンピューティング、その他のメモリスタやスピンエレクトロニクスデバイスの使用などが挙げられる。

メモリスタなどを使うアナログ型の神経回路は、けた違いにエネルギー効率が高い。また、神経科学とニューロコンピューティングが互いに両者を発展させるという関係も期待される。

量子コンピューティングには、量子ゲートを使いShorのアルゴリズムで計算を行なうタイプと量子アニーリングを使うタイプがある。Shorのアルゴリズムは因数分解などができ、実用的な量子コンピュータができれば威力を発揮するが、現状では、コヒーレンス時間が足りず、エラー訂正で補おうとすると、回路規模、消費電力が膨大になってしまう。

|

|

|

量子ゲートを使いShorのアルゴリズムで計算を行なうタイプと量子アニーリングを使うタイプがある。前者は、まだ、コヒーレンシを維持できる時間が短い。エラー訂正を使えばよいが、必要なqubit数が1000倍になり、消費電力も膨大になってしまう |

しかし、Level4のデバイスのテクノロジは、非常に未成熟な状態にある。また、これらのデバイスを使ってコンピューティングを行うためのシステムソフトウェアは、まったく存在しない状態である。したがって、Level4のアプローチを実用化するには、膨大な投資が必要になる。