Xeon Phi、IoT、ディープラーニングなどの新たなフロンティア

10年ほど前に、消費電力の制約からクロック周波数が上がらなくなり、主要な性能向上手段はプロセサの数を増やすマルチコア化ということになった。そして、Intelのサーバ向けプロセサのXeonのコア数も増え続け、現在では最大22コアというチップが作られている。

マルチコアで並列性を追求するXeon Phi

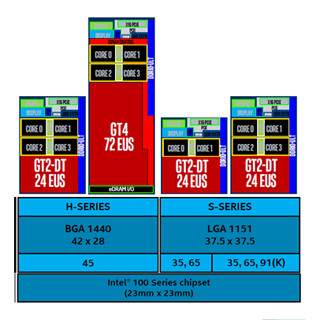

しかし、より高い並列処理性能の実現を目指して、IntelはXeon Phiというマルチコアプロセサを作っている。第1世代のKnights Corner(KNC)ベースの製品は最大61コア、第2世代のKnights Landing(KNL)ベースの製品は最大72コアとなっている。

KNCは、PCIe経由でXeonやCoreプロセサにアクセラレータとして接続するという使い方であったが、KNLは、PCIe経由のアクセラレータという使い方以外に、これをホストプロセサとして使う製品が出る計画になっている。ホストプロセサとして使う場合はXeonを使わないシステム構成も可能であるが、Xeon PhiとXeonをネットワークで接続するヘテロなクラスタとして使うことも想定されている。

Xeon PhiをアクセラレータとしてPCIe経由で接続する場合と、ホストプロセサとして使う場合を比較したのが、次の図である。

外部接続は、アクセラレータの場合はPCIe、ホストプロセサの場合はOmniPathが使われる。また、アクセラレータの場合は、メモリが最大16GBに制限されるが、ホストプロセサとして使う場合はDDR4メモリが接続できるので最大400GBという大容量のメモリが使える点が大きな違いとなっている。

KNCチップは最大72コアで、各コアは512バイト幅の積和演算を実行できるVPUを2個搭載している。32bit長の単精度浮動小数点演算の場合、ピーク演算性能は3TFlopsを超えると発表されている。72コアは2コアがペアとなり36個のブロックとなっており、これらの接続はXeonとは異なり2次元メッシュネットワークを使っている。

KNCはXeonとは命令互換ではなかったが、KNLではホストプロセサとして使うので、命令がXeonと互換になった。そして16GBのMCDRAMと呼ぶ、3Dスタックの高速メモリを接続する。MCDRAMを使うと、DDR4メモリを使う場合に比べると、Streamベンチマークの性能は5倍以上に向上するという。

そして、ホスト型の製品では、 OmniPathファブリックのインタフェースチップをKNLチップと16GBのMCDRAMを搭載するマルチチップパッケージに搭載している。

MCDRAMと3D XPoint技術でメモリ階層を改善

次の図はメモリ階層を示すもので、左が通常のシステムのメモリ階層、右が将来のシステムが目指すメモリ階層である。MCDRAMをプロセサパッケージに搭載して最初の外部メモリをプロセサに近づけてメモリバンド幅を改善し、3D XPoint技術を使うDIMMで、メインメモリの容量を大幅に増加させる。これで大量のデータを扱う処理の性能を大きく改善できる。

また、3D XPoint技術を使うIntelのOptane SSDでBurst Bufferを作り、I/Oノードに付けられていたストレージ機能の一部をコンピュートノードに入れ込む。これによりストレージの階層を短縮し、性能を上げることができる。

|

|

MCDRAM技術でメモリバンド幅を5倍に改善し、3D XPoint技術でメインメモリの容量を10倍にする。また、これらの技術でストレージの階層を短縮しBurst Bufferの追加などで性能を引き上げる |

MCDRAMは、DDR4と比べるとバンド幅は5倍、GDDR5と比べるとエネルギー効率は5倍以上で密度も3倍以上である。CPUと同じパッケージにMCDRAMを搭載することで、DDR4より5倍程度高バンド幅となり、CPUとメインメモリの間のギャップを埋めることができる。

3D XPointはNAND Flashと比べると速度は1000倍、書き込み寿命も1000倍。そして、DRAMと比べると密度は10倍である。この技術をDDRの10倍の密度のDIMM、1000倍高速のSSDとして応用すれば、DRAMメモリとストレージの間のギャップを埋めることができる。

MCDRAMや3D XPointメモリはメモリ階層のギャップを埋め、計算処理に新たなフロンティアをもたらす。