「RISC-V(リスクファイブ)」はオープンなプロセサアーキテクチャで、学術や教育的な用途だけでなく、商業的にも無償で利用できる。元々は、コンピュータアーキテクチャ学習のバイブルとも言えるヘネパタ本で、コンピュータを教えるために作られたDLXというアーキテクチャが原点で、これが、順次、改良された第5版がRISC-Vというわけである。

|

|

|

RISC-V Foundationの会長のKreste Asanovicカリフォルニア大学教授 (出典:RISC-V FoundationのWebサイト) |

RISC-Vアーキテクチャは、もともとはカリフォルニア大学バークレイ校で開発されたものであるが、教育用だけに使うのはもったいないので、実用に使えるようにしようとRISC-V Foundationという団体を作って普及に乗り出している。

RISC-Vには32bit版と64ビット版があり、それぞれに整数演算だけの基本アーキテクチャと乗除算拡張、アトミック拡張、単精度浮動小数点拡張、倍精度浮動小数点拡張のように分かれており、必要な拡張だけを選択して実装することができるようになっている。

また、単に、アーキテクチャを無償でライセンスするだけでなく、Rocketコアという5段パイプラインのインオーダ実行コアの設計も公開している。

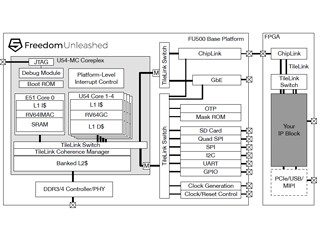

さらにカリフォルニア大学の開発者たちが作ったSiFive社は、2017年8月に開催された「Hot Chips 29」において同社のRISC-V製品に関する発表を行った。それによると、Coreplexと呼ぶCPUのIPとFreedomと呼ぶ周辺機能を集積したSoCを開発し、ライセンスを行っている。

一般に、SoCを開発する場合、CPUコアだけでなく、メモリコントローラ、PCI Express、USB、EthernetなどのIPが必要になり、これらのIPをメーカーからライセンスを受けるには多額の初期費用が必要であるが、Freedom SoCの場合、SiFive社が間に入って一括ライセンスをすることにより、ユーザの初期費用は少なく抑えて、製品化を行ったらライセンス料を払うというやり方をとることが出来る。

この場合、開発の初期に高いライセンス料を払う必要がなく、SoC開発の敷居が低くなり、カスタムチップの開発が促進されるという。

RISC-V Foundationは12月18日、東京大学本郷キャンパスにある伊藤謝恩ホールで「RISC-V Day 2017 Tokyo(日本名:RISC-Vの1日)」というRISC-Vを紹介するイベントを開催する。RISC-V開発の中心人物で、RISC-V Foundationの会長であるKreste Asanovic教授も来日して講演を行うほか、SiFive社のマーケティング担当VPのJack Kang氏やEsperanto Technologies社の笠原栄二氏などが講演を行う予定となっている。Esperanto社はステルスモードで活動しているスタートアップで、今回の講演で、果たして何をやっているのかがどこまで語られるのかが興味深い。なお、笠原氏は、ソニー・コンピュータエンタテインメント社(SCE)の技術ディレクタ時代に、プレイステーション3用のマイクロプロセサ(CELL/B.E.)の開発に従事した人物で、8月にHot Chipsでお会いした時は、まだ、ソニー系の会社に居られたが、その後、Esperantoに移られたようである。

なお、会費は有料で、一般が4800円(当日5000円)、学生2800円、レセプション費用3500円となっている。