産業技術総合研究所(産総研)は6月5日、ゲルマニウム(Ge)の膜厚10nm以下の均一な超薄膜構造の作製法を開発したと発表した。このナノメートルレベルの均一なGe超薄膜を絶縁膜で挟むと、Ge超薄膜中の電子移動度が著しく向上することも明らかになっている。

同成果は、産総研ナノエレクトロニクス研究部門 Wen Hsin Chang特別研究員、3D集積システムグループ 入沢寿史主任研究員、同研究部門 前田辰郎研究主幹らの研究グループによるもので、詳細は6月5~8日に京都で開催される「2017 VLSI Technologyシンポジウム」にて発表される。

Geは、従来の大規模集積回路(LSI)で用いられているSiに比べて移動度が高く、より低電圧で多くの電流を流すことができることから、SiをGeに置き換えることでLSIの高速化が可能となる。

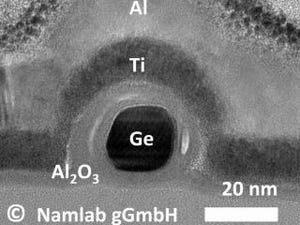

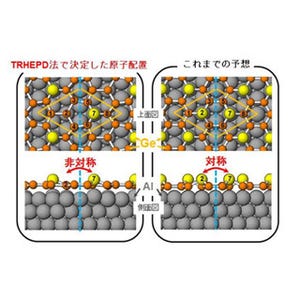

今回の研究では、半導体転写技術を高度化することによってGeの単結晶薄膜を作成する「HEtero-Layer Lift-Off (HELLO)法」を開発した。また同手法を用いて作成した単結晶Ge超薄膜の、膜厚13nmから3nmにおける電子移動度のシート電子密度依存性を確認したところ、13nmから3nmに薄膜化するにつれて電子移動度が急激に上昇する現象を発見。シート電子密度5x1012cm-2で、移動度は2.5倍にまで増加していることがわかった。従来、絶縁膜で上下を挟まれたSiやGeといった半導体薄膜では、上下の絶縁層と半導体薄膜の界面の不均一性や、半導体薄膜の膜厚揺らぎの影響が大きくなるため、5nm以下の膜厚では電子移動度が著しく減少することが報告されていた。

同研究グループは、今回の発見について、これまでの常識を覆す結果であり、高性能超低消費電力Ge-LSI実現だけではなく、新たな電子・光デバイスへの応用展開も期待されると説明している。