GLOBALFOUNDRIES(GF)は9月15日(米国時間)、14nm FinFETデバイスの次に、10nmをスキップして、7nm FinFETプロセスを採用したデバイスのリスク生産を2018年の早い時期から始めると発表した。なお、一般顧客が設計をするのに必要な技術提供は2017年後半から行うが、有力顧客のテープアウトは2017年末までに行う予定である。

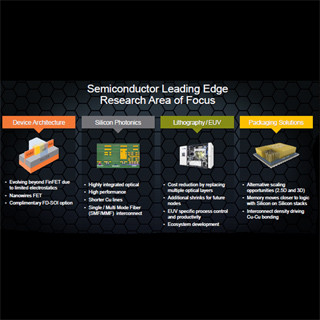

同7nm FinFETプロセスは、ファウンドリ各社で現在量産中の16/14nm FinFETプロセスを用いたデバイスに対して、ロジック密度を2倍以上に、性能を3割向上させることができるとしている。業界標準のFinFET構造を用いており、従来の光リソグラフィに加えて、一部のクリティカルレイヤにEUVリソを併用する。そのため、ニューヨーク州にある同社の最先端半導体工場であるFab 8(写真1)に露光装置などを数十億ドル規模で投資する予定だが、14nm FinFETデバイス用の製造装置やプロセスの多くも転用できるため、プロセス立ち上げを早められるとしている。

すでに有力顧客の7nm FinFETテストチップをFab 8にて流しているとするが、EUVリソについては当面の間、ニューヨーク州立大学College of Nanoscale Science and Engineering(CMSE)キャンパスに設置された同校とGF、IBM、東京エレクトロンなどとのコンソーシアム「Advanced Patterning and Productivity Center(APPC)」にて行う予定としている。

IBMとの協業で7nmプロセスを構築

GFのCEOであるSanjay Jha氏は、「7nmは、次世代の長く使い続けられる技術ノードであり、ここで他社に差異を付けられるのは、IBMからGFに移籍した優秀な人材とノウハウ、それに、IBMとの研究アライアンスによる世界トップクラスの研究開発体制によるところが大きい」と述べており、IBMもまた、7nmおよびそれ以降のプロセス技術の共同研究を加速するのに役立つ新しいアイデアやスキル、新技術の開発を今後も協力していくとしている。

また、米国ハイテク市場調査企業TIRIAS ResearchのプリンシパルアナリストであるJim McGregor氏は、「10nmをスキップして14nmから7nmへ直接移行するという決定は、ほかのいくつかの半導体企業も採用しようとしている。10nmは、コストがかさむ割に性能や消費電力の改善がわずかしか見られないからであるが、7nmは、2020年代、さらにはその先、長期に渡り使われる可能性を秘めている」と述べている。

12nmFD SOIと共存体制

7nmの設計に使うフィジカルIP(スタンダードセル)の開発は、14nm(14LPP)やFD-SOIプロセス(FDX)向けのフィジカルIPを開発した実績がある米INVECASが担当する。同社は、顧客に対して設計支援サービスも提供することになっている。

なお、GFは7nm FinFETプロセスの適用分野として、ハイエンドモバイルSocからクラウドサーバ、ネットワーク・インフラ用プロセッサなどの次世代の高性能コンピューティングを想定している。SOI基板を用いた、超低消費電力向けのプレーナー完全空乏型プロセス技術22FDX(22nm)、さらにはその先の12FDX(12nm)と補い合って、次世代デバイス用プロセスを提供していくとしており、今後、ファウンドリトップであるTSMCとの微細化競争が一段と激しくなることが予測される。