東京工業大学は11月30日、高分解能MEMS加速度センサーをCMOS-LSI直上に1チップ集積し、従来のMEMS技術では困難だった1G以下の高分解能検知ををワンチップのMEMSセンサーで実現したことを明かした。

同成果は同大異種機能集積研究センターの益一哉 センター長と山根大輔 助教、町田克之 連携教授、東京大学先端科学技術研究センターの年吉洋 教授、NTTアドバンステクノロジらの共同研究によるもので、11月上旬に韓国・釜山で開催された「IEEE SENSORS 2015」で発表した。

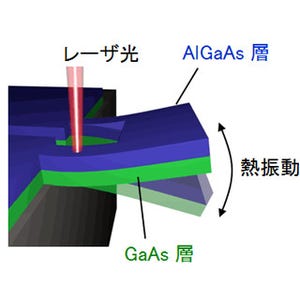

加速度センサーの検出性能は錘の質量に比例するため、錘サイズ小型化と検出分解能向上にトレードオフが生じる。従来のシリコンMEMS加速度センサーでは、高い検出分解能を得るために錘サイズが増大し、小型化が困難だった。また、汎用的な静電容量型加速度センサーを用いて微小加速度を検出する場合、寄生容量を大幅に低減する必要があるが、シリコンMEMS技術では錘サイズが大きく、センサー回路からなるLSIと集積する際に寄生容量が増大するなどの課題があった。

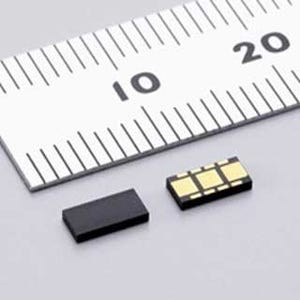

同研究では、高密度の金を錘に用いた小型・高分解能のMEMSデバイスをCMOS-LSI上にワンチップ集積化することで、従来のMEMS加速度センサーと同等のサイズで1G以下の高分解能検知を実現可能とし、錘サイズ小型化と検出分解能向上の両立に成功。MEMSとCMOS-LSIの集積化に半導体微細加工技術と電解金めっきを用いており、超小型・超高分解能加速度センサーの汎用化技術として期待できるという。

同研究グループは、超小型・超高分解能の小型加速度センサーの実現は医療・ヘルスケア、インフラ診断、移動体制御、ロボット応用などにおいて新しいデバイス・システム開発につながることが期待できるとしている。