日立製作所は2月23日、約1兆の500乗通りのパターン(組み合わせ)から適した解を導く「組み合わせ最適化問題」を量子コンピュータなみの性能で実現可能な新型コンピュータを試作したと発表した。

同成果の一部は、2015年2月22日~26日の期間で、米国サンフランシスコにて開催されている半導体集積回路に関する国際会議「2015 International Solid-State Circuit Conference(ISSCC 2015)」で発表される。

同コンピュータは、従来のコンピュータと同様に半導体素子を用いて動作するため、現在、量子コンピュータとして用いられている計算手法である量子アニーリングで必要となる冷却装置などを用いずに、室温で動作させることが可能だという。また、スケーリングも可能だという。

具体的には、半導体CMOS回路上で量子アニーリングで解を求めていたイジングモデルの振る舞いを擬似的に再現するCMOSアニーリング技術を開発し、外部から特殊な回路を経て入力されるノイズを利用し、特定の局所解への固定を防ぐことで、より良い解を求めるアニーリング動作を実現。また、解くべき最適化問題を、+1と-1の2つの状態を取る強磁性体スピンが隣接するスピン間で相互作用する振る舞いを示すイジングモデルで表現し、半導体メモリ技術を用いて実装することで実現したという。

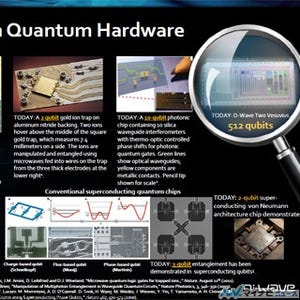

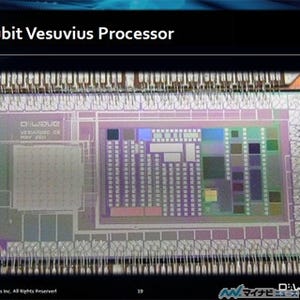

これらの技術は65nmプロセスを用いて開発され、研究では、2万480パラメータを入力可能なコンピュータの試作機を開発し、実証実験を実施。その結果、システムが室温で動作することが確認されたほか、現在の量子アニーリングを用いた量子コンピュータのパラメータ数512の40倍となる2万480パラメータの大規模な組み合わせ最適化問題を数ミリ秒で解けること、ならびに従来のコンピュータを用いて解く場合と比較して電力効率約1800倍を実現できることを実証したという。

なお同社では、現在実用化されている最先端半導体プロセスとなる14nmプロセスを用いた場合であれば1600万パラメータに対応するチップに大規模化することも可能だと説明している。