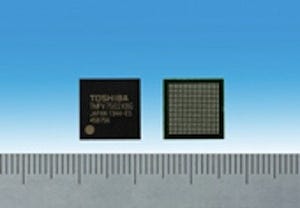

東芝は、フラッシュメモリとCMOSトランジスタを同一チップ内に近接して混載する技術を開発したと発表した。同技術をFPGAに応用することで、低消費電力かつ高性能な不揮発FPGAが実現する。

詳細は、ハワイにて開催された「2014 VLSI Technology シンポジウム」で6月10日(現地時間)に発表された。

近年、カスタムLSIの開発コストが増大しており、チップ製造後に回路情報を任意に書き換えることができるFPGA市場が拡大している。FPGAは主に演算を行うロジック素子と、回路情報の記憶を行うメモリで構成されている。高性能FPGAはロジック素子に揮発性のメモリであるSRAMを用いているため、消費電力が大きいという課題があった。これを解決するため、不揮発性のフラッシュメモリを用いたFPGAが望まれていた。しかし、フラッシュメモリとロジック素子に内蔵されるCMOSトランジスタは、素子構造と動作電圧が大きく異なるため、同一チップ内への混載が困難だった。

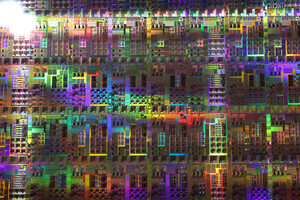

そこで今回、通常用いられているフラッシュメモリと異なる構造を持つMONOS型フラッシュメモリを適用し、書き込み手法と回路構造を工夫して、CMOSトランジスタとフラッシュメモリを近接して混載する技術を開発した。これにより、従来のSRAM型FPGAと同等の高速動作を実現しつつ、動作中の消費電力を削減することができ、メモリの占める面積も半分に削減したという。

SRAMをMONOS型フラッシュメモリに置き換えたことで、電源の供給を止めてもデータを失わないため、FPGA動作中にチップ内で使用していない領域の電源を部分的に遮断し、無駄な電力消費を削減できる。東芝のテスト回路における試算では、ロジック使用率が80%の場合で、SRAM型FPGAに比べて約40%の電力削減が見込まれたという。また、フラッシュメモリへの書き込みの際に大電圧を使用しても、CMOSトランジスタの特性を悪化させないホットエレクトロン現象を利用した書き込み手法と回路構造を採用したことで、性能を維持している。

同技術は、東芝社内で活用する他、協業可能な企業へのライセンスも視野に検討していく。また、今回開発した技術をはじめとして、今後もフラッシュメモリ技術の応用範囲拡大を目指し、研究開発を進めていくとコメントしている。