計測機器大手Agilent Technologiesの日本法人であるアジレント・テクノロジーは6月10日、同社の「Advanced Design System 2013(ADS 2013) Transient Convolution Element」および「SystemVue 2013 AMI Modeling Kit」で利用可能な、数Gbpsの高速チップ間通信での信号歪みによって引き起こされる問題解決に対応可能な機能拡張版リピータ・モデル・ライブラリを提供することを発表した。

数Gbpsを超すチップ間のデジタル信号通信は、FR4などの材料の基板上では、数インチ伝送しただけで、信号が劣化するという課題があり、対策として高周波のラミネート基板の利用などが考えられるが、コストが高くなってしまうといった課題があった。コスト面を現実的に考えた場合の解決策としては、チャネルに、減衰した信号の補償機能やジッタの減少機能を有するリタイマ回路を挿入する方法があったが、シミュレーションツールにはキルヒホッフの電流法則の節点解析についてニュートン・ラフソン法による反復計算を行うSPICEシミュレーションが用いられていたこともあり、解析に多くの時間が必要となっていた。

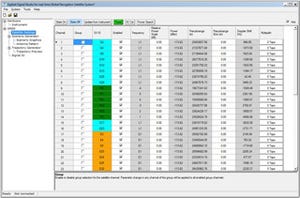

今回、同社が提供するリタイマ・アプリケーションでは、ビットごとのチャネル・シミュレーションと業界標準のIBIS AMI フローを元にしたソリューションで、解析に要する時間を削減することが可能となるとする。また、ADS 2013では、IBIS Power BIRDs、Touchstone 2ファイル形式にも対応しているほか、Touchstone Combiner機能を搭載しており、4ポート ベクトル・ネットワーク・アナライザの測定データを利用して、4ポート以上のクロストーク解析用チャネルモデルを構築できるようになったとする。

なお、同社では今回の手法を将来のIBIS標準に盛り込むため、2013年末に開催されるIBIS Open Forumに機能拡張の提案書を提出する予定で、もし、これが実現すれば、将来はリタイマ・モデルを対応するEDAツール間で共有することが可能になるとしている。