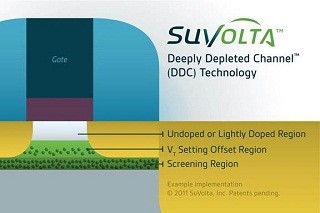

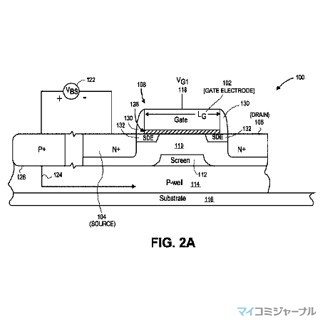

米SuVoltaは、12月10日から米サンフランシスコで開催されている「2012 International Electron Devices Meeting(IEDM 2012)」において富士通セミコンダクター(FSL)と共同で「DDC(Deeply Depleted Channel:深い空乏層を利用するチャンネル)」技術の性能と消費電力の優位性をシリコン上で実証した結果を発表した。

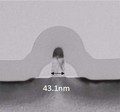

同成果は、SuVoltaの低消費電力CMOSプラットフォーム「PowerShrink」をFSLの65nm低消費電力プロセスに作り込んだアナログとデジタルの回路とFSLの標準プロセスで作った回路とを比較したもので、デジタル回路では、DDC技術では電源電圧VDDが1.2Vの時に消費電力を標準回路と同じにしたところ、性能が30%増加したことが確認された。また、VDDを0.9Vにして、性能を同じにしたところ消費電力が47%減少することも確認された。これらのDDC技術を採用したデバイスのパラメータには、バラつきが改善されたチップ全体および一部分のしきい電圧VTと、高いボディ係数、高い有効電流IEFFが含まれているという。

この結果から、DDC技術は設計上の要求により高速動作にも低消費電力動作にも対応できることがシリコン上で実証されたこととなる。なお、FSLでは、期待通りの結果が得られたとのことから、同技術を55nmプロセスに使った製品を2013年上期に提供開始する予定としている。