Alteraは、自社のFPGA開発ソフトウェア「Quartus II」の最新版となる「Quartus II ver.12.0」を発表した。コンパイル時間を最大4倍高速化した他、28nm製品サポートを拡充している。

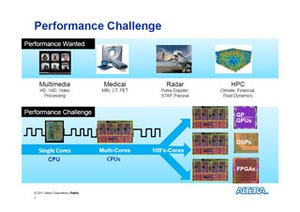

同バージョンでは、アップグレードされた点として、ハード・デュアルコア「ARM Cortex-A9」を搭載する同社の「SoC FPGA」のイニシャル・サポートがなされたほか、28nm FPGAデバイス・サポートの拡大、「Qsys」システム統合ツールならびに「DSP Builder」ツールの機能拡張、および改良されたIPコア製品群の提供が含まれている。

業界最速クラスとなるコンパイル時間を実現。これにより生産性を高めながら、リソースを製品開発に集中させることができるようになると同社では説明している。従来バージョン製品と比較して、「Stratix V」ユーザーはコンパイル時間を平均35%、「Cyclone V」および「Arria V」ユーザーは平均25%削減が可能だという。また、広範な低コスト、ミッドレンジ、ハイエンドの28nm FPGA製品群の中から、最適なデバイスを選択して設計を行うことができる。

「Qsys」システム統合ツールでは、ARM AMBA AXI-3インタフェースへのサポートが追加された。「Qsys」は、Network-on-a-Chip(NoC)技術を使ったシステム統合ツールで、高性能接続を可能とする。また、異なる標準インタフェースを利用しているIPコアおよびIPサブシステムを、柔軟に接続させることが可能。さらに、階層化アプローチによって、IPファンクションとIPサブシステムを統合することで、システム開発を容易にするできる。このほか、同バージョンでは、システム設計者による自動化を支援し、デザインの再利用を容易にする機能が多数含まれているという。

この他、新しいDSPのサポートにより、MATLABからシステム・コンソールを介して、DDRメモリへの通信が可能になったほか、新しい浮動小数点機能が搭載され、デザインの生産性とDSPの効率向上がなされた。ビデオ/画像処理スイート(VIP)と、ビデオ・インタフェースIPの機能拡張では、エッジ適応アルゴリズムや、新しいAvalon-Streaming(Avalon-ST)Video Monitor、Trace System IPコアを、アップデートされたScaler II MegaCoreファンクションと併用することで、ビデオ処理アプリケーションの開発容易化を実現した。また、トランシーバ・デザインおよび検証の機能拡張では、アップデートされたトランシーバ・ツールキットにより、「Arria V」のトランシーバと、「Stratix V」の14.1Gbpsまでのハイスピード・トランシーバ・データーレートのサポートが追加された。

なお、同バージョンのサブスクリプション・エディション、ならびに無償のWebエディションはともに、同社のWebサイトから入手可能だ。「Quartus II 開発ソフトウェア サブスクリプション契約」には、開発ソフトウェア「Quartus II」、「ModelSim Altera Starter Edition」、同社のIPコアとしては最もよく利用されている15個のIPコア(DSP機能とメモリI/F)で構成される「IP Base Suite」の全ライセンスが含まれている。年間費用は、米国内販売価格で2995ドル(ノード・ロックPCライセンス時)で、同社のeStoreまたは販売代理店から購入できる。