早稲田大学(早大)は4月25日、組み込み機器からスーパーコンピュータ(スパコン)まで幅広く使われる各種のマルチコア(ホモジニアスマルチコア1およびヘテロジニアスマルチコア2)、メニーコア、共有メモリ型マルチプロセッササーバ上で、並列プログラムを高速かつ低消費電力で動作させることができるソフトウェア標準「OSCAR API ver.2.0」を開発したと発表した。

同成果は、同大理工学術院の笠原博徳教授らのグループ、早稲田大学グリーンコンピューティングシステム研究機構アドバンストチップマルチコアプロセッサ研究所内に設置されたマルチコア・メニーコア・アーキテクチャ・アプリケーションAPI委員会にて、イーソル、オリンパス、ガイオ・テクノロジー、キャッツ、デンソー、東芝、東邦大学、名古屋大学、日本電気、日立製作所、富士通研究所、三菱電機、ルネサス エレクトロニクス、ルネサスソリューションズの12社、3大学によるもの。

この標準「OSCAR API ver.2.0」は、NEDOプロジェクトで開発し、2008年11月14日に公開したホモジニアスマルチコア用「OSCAR API ver.1.0」を発展させたもので、CおよびFortran言語用のコンパイラ指示文の集合体となっている。これにより、ホモジニアスマルチコアに加え、ヘテロジニアスマルチコア、キャッシュコヒーレンス制御機構を持たないメニーコア、共有メモリ型マルチプロセッササーバー上でも動作する高速・低消費電力の並列プログラムを簡単に作成できる。

「OSCAR API ver.2.0」で記述された並列プログラムは、早稲田大学OSCAR並列化コンパイラにより、逐次プログラムから自動生成することができ、マルチコアで問題となるソフトウェアの開発コスト・開発期間を大幅削減できる。またユーザによる、並列プログラムの手動作成も可能となっている。

「OSCAR API」では、電力制御指示文が用意されている。これを用いて、CあるいはFortranプログラム中から、各プロセッサコア、メモリ、コネクションネットワークの動作周波数、電圧、電源遮断も行えるため、チップ消費電力の大幅な削減に寄与する。さらに、自動車などの組み込みシステムで要求されるハードリアルタイム処理を行うためのタイマ管理機能、ローカルメモリ、DMAC(データ転送ハードウェア)制御指示文も用意されている。

また、同APIで記述された並列プログラムは、異なるメーカーのマルチコア間で簡単に移植できる。これにより、各種製品の開発サイクルの短縮、スマートフォンなどの低消費電力化可能となる。

マルチプラットフォーム化に関しては、現在までにSuperH/ARM/FR-V/V850/SPARC/Intelプロセッサ/AMDプロセッサ/IBM Powerプロセッサなど、OSに関しても、Linux/AIX/Solaris/Windows/eT-Kernel/Multi-Core Edition/LWOS3上での動作が確認されている。

マルチコア、メニーコアあるいはマルチプロセッササーバ上で、APIで並列化されたプログラムを動作させるのは、当該プロセッサ用の逐次コンパイラと、早稲田大学より無料配布されるAPI解釈系があれば簡単に行える。このため、巨額の費用が必要な当該チップ用並列化コンパイラの開発、あるいは並列APIをサポートするためのコンパイラの修正などが不要となる。サーバ上でも、逐次コンパイラが用意されていれば、プログラムの並列実行が可能。また、OpenMPでは定義されていない電力制御あるいはDMACを用いたデータ転送などの指示文がコメント文として扱われるようになっているため、OSCAR APIで記述された並列プログラムは、OpenMPコンパイラを用いても簡単に実行できる。生成された並列プログラムのデバッグには、各種市販ツールがそのまま利用できる。

具体的に、「OSCAR API ver.2.0」とOSCAR並列化コンパイラを用いた高速化および電力削減が実現された成果を以下に挙げた。

- AACエンコード(オーディオデータ圧縮)をSH4Aベース8コア・ホモジニアスマルチコアRP2(日立・ルネサス・早大で開発)上でリアルタイム処理した際、消費電力を1/9に削減。

- デジタルテレビで使われるMPEG-2デコードのRP2上でリアルタイム処理した際、電力を1/4に削減。

- ルネサスNaviEngine4コア(ARM MPCore)Linux上で、MPEG-2エンコードを逐次に比べて3.6倍高速化。

- 3コアNaviEngineリアルタイムOS eT-Kernel上で、AACエンコードを逐次に比べて2.9倍高速化。

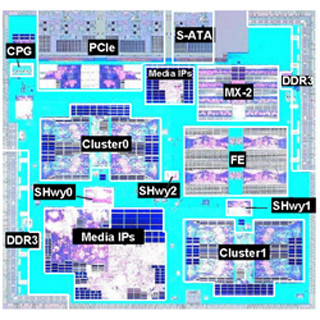

- ヘテロジニアスマルチコアRPX(日立、ルネサス、東工大、早大で開発)上でのオプティカルフロー計算(動画像において移動する物体を追従するプログラム)において、8つのSH4Aプロセッサと4つのアクセラレータFEGA(動的再構成可能プロセッサ)利用時に逐次に比べ33倍高速化。

- RPX上で、リアルタイムオプティカルフロー計算の消費電力を1/3に削減。

- 富士通FR-Vプロセッサベースの4コアマルチコアFR1000、およびルネサスSH4Aベースの4コアマルチコアRP1上で、各種マルチメディア処理を1コアに比べ平均3.4倍高速化。

- 8コアRP2マルチコア上で、OSCAR並列化コンパイラによる自動ソフトウェアコヒーレンス制御により、MPEG-2エンコードを逐次に比べ6.6倍高速化。

- 富士通 SPARC Enterprise M9000(SPARC64 VIIベース64コアSolaris SMP)上で、SPEC2000 171.swimベンチマークプログラムを逐次に比べ36倍高速化。

- 日立SR16000(Power7ベース64コアLinux SMP)上でGMS4地震波伝搬シミュレーションを逐次に比べ41倍高速化。

- SR16000上で三菱電機重粒子線ガン治療装置用線量計算を、逐次に比較し55倍高速化。

「OSCAR API ver.2.0」の仕様は、笠原研究所のWebサイトで公開されており、無料でダウンロードできる。