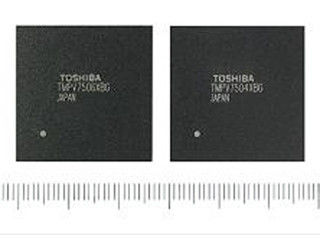

東芝は、携帯機器などの消費電力削減に有効な、0.5Vから1.0Vの広い範囲の電圧で動作する混載SRAM回路技術を開発したことを発表した。同成果は、半導体国際学会「A-SSCC2011」において発表された。

今回試作したチップは40nmプロセスを採用した2Mビット品で、動作電圧が変化してもSRAMが正常に動作できるように3種類の新しい技術を採用し、同時にセル不良率の低減と高速化も実現した。

モバイル機器向けLSIに用いられる混載SRAMはデータを格納するために必要な大量のSRAMセルを搭載しており、その個々の特性がバラついても安定した性能を実現することが求められる。また従来のSRAM技術ではワード線でデータの読み出しや書き込みを行っているが、トランジスタのしきい値や温度、電圧といった動作条件が変動すると、SRAMセルが正常に動作する最適なワード線の電圧も変動することから、今回、リアルタイムにSRAMセルの不良率を予測し、これらの動作条件が変化してもSRAMセルの記憶を保持できるようにワード線の電圧を自動的に設定する回路を新設した。

これによりセル不良率を従来比1/100に低減することに成功したという。また、同回路の新設により、従来行っていたワード線レベルの電圧をチップごとに設定する工程を不要としたという。

また、SRAMでは、センスアンプの起動タイミングを低電圧動作時の最も遅いセルに合わせてしまうため高速化が抑制されてしまうという問題があった。センスアンプの起動タイミングは電圧が高くなるほど早く設定できることから、今回、各動作電圧時の最も遅いセルに起動タイミングを合わせる回路を搭載することで、どの動作電圧でも最適なタイミングでの起動を可能とした。この結果、従来比18%の高速化(1.0V、室温動作時)に成功したという。

さらに、低電圧時には読み書きをする際にビット線にSRAMセルが影響されて誤作動するという問題があるが、従来1本ずつ選択していたワード線を8本同時に選択し、同一データを読み書きすることで、利用できるメモリ容量を縮小する代わりに0.5Vの低電圧での動作を可能とした。

これら3つの技術を組み合わせた結果、広範囲の動作電圧に対応することが可能となり、0.5V動作時で従来比最大57%の消費電力削減が実現されたという。

なお、同社では今後、同技術の開発を加速し、携帯機器などの広範囲の電圧変化に対応できるLSIが必要とされる機器向けの製品への早期搭載を目指すとしている。