|

|

Tabulaの創業者でPresident&CTOのSteve Teig氏 |

Spacetimeアーキテクチャに基づく3-D Programmable PLD(3PLD)の提供を行う半導体ベンチャーの米Tabulaは10月18日、都内で会見を開き、Tabulaの創業者でPresident&CTOのSteve Teig氏が同社のビジネスの目指すところと、自社のアーキテクチャに関する説明を行った。

3PLDについて同氏は「新たなクラスのプログラマブル・デバイス(PLD)」と表現し、「従来型のFPGAを超える性能を実現するデバイスの実現を目指している」と説明する。同氏はもともとEDAツールベンダのCadence Design SystemsのCTOなどを務めた人物で、同社のアーキテクチャには同氏のソフトウェア畑での経験がふんだんに盛り込まれたものとなっている。

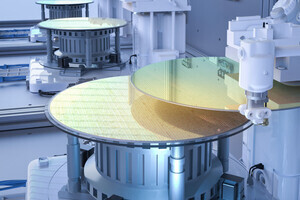

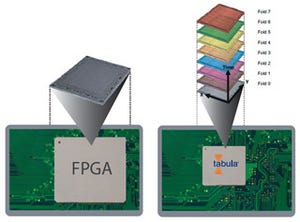

特に同社のコアテクノロジーとなる「Spacetime」アーキテクチャには同氏の思想がふんだんに盛り込まれたものとなっている。従来の半導体はダイを拡大することで、トランジスタ素子の数を増やし性能を向上させてきた。しかし、それではダイサイズが大きくなり、ウェハ1枚あたりからの取れ数も減るし、チップサイズ(フットプリント)も大きくなってしまう。

こうした課題に対する答えの1つが同アーキテクチャで、概念的に複数レイヤの3D構造を疑似的に作ることにより、ダイサイズを小さくしつつ、素子数などは従来のFPGAと同等か、それ以上の性能を実現しようというものとなっている。具体的には、使い勝手は競合となるXilinxやAlteraのツールと同様のものを意識して作成された専用コンパイラ「Stylus」にて一般的なFPGAのようにVerilog/VHDLにて1枚の回路レイアウトを構成、それをStylusのアルゴリズムが自動的に8枚のレイヤに分割し、その分割された回路レイアウトデータを時間軸のビア(クロックビア)を介して1.6GHzのクロックにて、ユーザー側のクロックと同期させて切り替えるというものとなっている。

200MHzのユーザークロックであれば、1枚の回路レイアウトをちょうど8枚分割で200MHz×8=1.6GHzで駆動させることが可能となる。こうして高速に回路を切り替えて、順次、演算を行うことにより、従来のFPGAに比べて、現行世代(TSMC 40nmプロセス)のABAX製品はメモリ集積度で2.0倍、ロジック集積度は2.5倍、メモリスループットは3.0倍、DSP性能は3.7倍に高めることができるという。

こうした性能を武器に、同社が狙う市場はまずは通信機器への搭載だという。「すでに日本の大手通信企業が興味を示している」(同)とのことで、日本での採用の可能性も高いという。また、日本市場は重要市場と同社でも認識を示しており、2011年6月1日付で日本支社を設立したほか、ルネサスイーストンによる受託開発などの提供も開始している。

「なぜ通信市場か、という疑問があるだろう。それは、同市場がFPGAで最大の市場で、また無線でも有線でも今後も成長が見込めるためだが、その一方で、爆発的に増加するデータの処理のためのパフォーマンス、I/Oなどの部分の対応などが求められるようになり、その課題を解決するためのソリューションが求められているからだ」(同)と、通信市場を最初のターゲットに据えた理由を説明しており、同市場でビジネスの足場を確保し、随時、ほかの市場にも展開を図っていきたいとする。

また、「2012年中には第2世代製品の提供を目指す」としており、当初予定していた4製品のうち、最大LUT数の「A1EC06」の開発をキャンセルし、そのリソースも第2世代品の開発に振り分けなおすなど、開発の加速を行っている。「現時点で、第2世代のことで言えることは、より高速に回路の切り替えが可能になる、ということだ。回路の切り替え速度が速くなれば、それだけ少ない面積でより高い性能を実現することが可能となる。ムーアの法則がプロセスの微細化の限界が見えてきて、終息するのではないかと危惧されるようになってきた現在、ダイサイズの小型化による低コスト化とパフォーマンスのさらなる向上の両方を実現できるアーキテクチャを我々は考案した。マネジメントチームは、これまでFPGA業界で実績を持つ面々が集まっている。第2世代品の早期立ち上げにより、競合優位性を発揮し、ASIC/ASSPとの差もさらに埋めていけるようにするつもりだ」(同)と、マネジメント面でも不安要素はなく、2012年が大きな飛躍の年となることを強調した。