米Open-Silicon、MIPS TechnologiesとDolphin Technologyの3社は共同で、TSMCの40nmプロセス上で2.4GHz駆動を可能にするASIC向けのプロセッサがテープアウトしたことを発表した。これはTSMCのリファレンスフローを使うという条件下ではもっとも高い動作周波数であり、より高性能なCPUを必要とするASIC向けとなるものだ。Open-SiliconとMIPSは2009年末に65nmプロセスを使ったテストチップで1.1GHz駆動を実現しており、今回の発表はこれに続くものとなる。

このプロセッサはOut-of-OrderとSuperscalarを実装したMIPS32 74Kfを利用しており、さらに高性能なFPUとDSP拡張を内蔵し、32KBの命令/データL1キャッシュおよび8KBのPDtraceを搭載する。MIPS32 74Kコアは完全シンセサイザブルであり、15段パイプラインにより高動作周波数で駆動可能なIPコアとして、ハイエンドコンシューマ機器からSTB、ホームネットワーク機器など広い範囲で利用されている。

65nmプロセスを使ってのテストデザインでは、MIPSがRTLデザインを提供、ここにDolphinの提供するメモリを組み込んだ形でOpen-Siliconが設計を完了させた。TSMCはこれを、CyberShuttleプロトタイピングプログラムを利用して製造している。

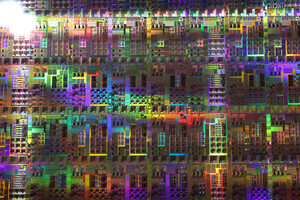

40nmプロセス世代に関しては性能を最大限に引き出すため、Open-Siliconは同社のCoreMAXテクノロジを利用して利用するライブラリの最適化を行なった。例えば今回の場合、MIPS32 74KfコアとFPU内部のクリティカルパスの最適化のために、159の新しいLVt cellと147のRVt cell、147のHVt cellがCoreMAXにより生成された。またこの他にもOpen-Sliconの得意とするプロセッサのフロアプラニング、スキューを考慮したクロックツリー生成、およびタイミング最適化などが採用されている。最終的な物理設計はCadenceのEDA layout toolが利用された。

なお、MIPSのCEO兼社長のSandeep Vijはこの取り組みについて「74Kコアは40nmプロセスを使ってのテストチップ製造に最適な選択だった。Open-SiliconとDolphinとの協業により、構成で2.4GHz駆動が達成できたことを嬉しく思う。そしてこの数字は40nmのみならず28nmプロセスにおいても、(74Kf以外の)IPコアでも実現可能であると考えている」とコメントしている。