5月11日、日立情報通信エンジニアリング(日立JTE)は同社のシステムレベル検証プラットフォーム「LogicBench」の第6世代製品を発表、即日出荷を開始した。これに先立ち、同社とザイリンクスは共同で記者説明会をザイリンクス社内で開催、製品の詳細について紹介を行った(Photo01,02)。

|

|

|

Photo01:冒頭挨拶を行った中野哲夫氏(日立情報システムエンジニアリング エンベデッドテクノロジ事業部 事業部長) |

Photo02:製品紹介を行った山口由二氏(日立情報システムエンジニアリング エンベデッドテクノロジ事業部 事業部長付) |

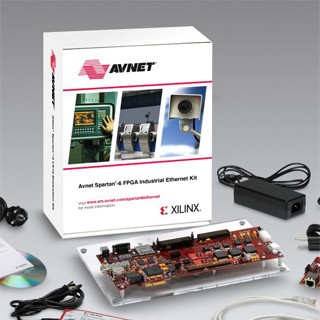

LogicBenchは、XilinxのFPGAを搭載した、ASICの製造に先立って設計検証などを行うプロトタイピングボードである。ただし第4世代の製品から、VirtualTurboと呼ばれるハードウェア/ソフトウェアの協調開発ツールも同時に提供されるようになり、今回提供されるVirtualTurbo-IIIでは仮想プロトタイピング連携までが視野に入ってきた(Photo03)。

|

|

Photo03:LogicBenchは当初からXilinxのFPGAを搭載するという形でXilinxと協業をおこなってきており、今回もVirtex-6を搭載する形で利用可能ゲート数を大きく増やしている |

そもそものLogicBenchは、Photo04にあるようにASICを使ってのシステム開発をより迅速に行うという目的で開発されたものである。ただしこれまでは単にFPGAを使って動作を検証するといった、低レベルのプロトタイプでの利用がメインであったが、VirtualTurboの機能強化により、ESL設計の仮想プロトタイピングから利用できるようになった。

|

|

Photo04:こうしたFPGAを使ってのASICプロトタイピングは、従来のハイエンドFPGAの主要な用途の1つであり、現在もまだASICビジネスが続いている以上、こうしたツールは必須である。かつてはASICを1回作り直すのは1,000万~数千万円のオーダーで可能だったが、最近は1回作り直すのに数億~数十億のオーダーになっており、到底作り直しが許されないからだ |

今回発表されたLogicBenchそのものは、2個ないし4個のVirtex-6が搭載されたドーターカードの形式である(Photo05)。実際のボードはPhoto06~08のような具合であり、4個のものでは2,400万ASICゲート相当の論理規模を確保できる。もちろん個々のVirtex-6は最大でも600万ASICゲート相当なので、適当に回路を分割して複数のFPGAに割り振ることになるが、これはLogicBenchが自動で行うため、ユーザーは分割を意識する必要が無い。

|

|

Photo05:配線を見ると判るとおり、複数のドーターカードをスタックして使える構造になっている。理論上はいくらでも積み重ね出来るそうだが、一般には2~3枚程度を上限とし、それより増やす場合はコンサルテーションという形になるとか。実際にはVirtualTurbo自身が複数個用意され、その上にこのモジュールがそれぞれ複数枚積み重なるといった構造をとっているケースもあるそうだ |

一方のVirtualTurbo-IIIは、LogicBench自身も搭載するほか、LogicBenchのマザーボードとして動作する(Photo09,10,11)

これを使っての実際の開発例としては、例えば3,000万ゲートを超えるようなASICの開発を迅速に行うケース(Photo12)や、より上流のESL設計(Photo13)への適用などが示された。

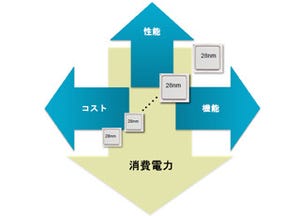

ところでおもしろいのは、LogicBenchは必ずしも最終ターゲットがASICとは限らないとの話である。昨今ではASICの開発費(というか、設計費用もさることながらASIC量産のために必要な初期コスト)が高騰しており、設計開始段階でASIC化を行うかどうか、決めかねる場合もあるという。ところがLogicBenchを使う場合、最終ターゲットをASICにするか、FPGAのままインプリメントするかを決めずに設計やプロトタイプ開発を行うことも可能であり、最後の段階で決めるということも可能だとしている。もちろん実際には動作速度などの制約もあるから、中には「プロトタイプはともかく量産時はASICにしないと性能的にマッチしない」というケースもあるだろうが、このあたりの自由度を確保できるという意味でも設計の柔軟性向上に繋がることになる。

これに関してザイリンクスのサムローガン社長によれば、「FPGAのマーケットが年間4,000億円程度、ASICはざっくり10倍程度といわれているが、ASICのマーケットは次第に縮小傾向にあり、逆にFPGAのマーケットは次第に増えつつある」との事。とはいっても、だからといっていきなりASICのマーケットが完全にFPGAで置き換えできる訳ではなく、先ずはプロトタイプツールとしてFPGAを広く使ってもらう形で入ってゆくことになり、この観点でLogicBenchは非常に有力なツールである、との事であった。

すでにLogicBenchは60サイトに500モジュール以上が販売されており、通信機器や携帯機器、車載機器、プリンタ、アミューズメント、医療機器、研究機関など非常に幅広い分野で導入されているが、同社によればこの第6世代のLogicBenchも100モジュール以上販売したい、との事であった。

この第6世代LogicBenchとVirtualTurbo-IIIは、12日より東京ビックサイトで開催される第13回 組込みシステム開発技術展(ESEC)にて、日立情報通信エンジニアリングのブースでデモンストレーションが実施される予定だ。