富士通マイクロエレクトロニクス(FML)、イー・シャトル、ならびに電子ビーム(EB)直接描画技術向け設計およびソフトウェアの提供を行う米D2Sは10月9日、D2SのEB直描技術向けLSI設計環境「DFEB(Design for e-beam)テクノロジ」をFMLならびにイー・シャトルが採用し、開発、実証を行うことで合意したことを発表した。

|

|

|

イー・シャトル代表取締役社長の土川春穂氏 |

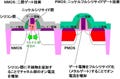

現在、可変整形ビーム(VSB:Variable Shaped Beam)方式によるEB直描の処理能力は「300mmウェハの全面露光で0.1wph程度」(イー・シャトル代表取締役社長の土川春穂氏)である。GDS(設計データ)の段階で、多く用いられる図形を抽出し、定型パターンをあらかじめ電子線露光マスク(ステンシル)として用意することで、露光のショット数を減らす部分一括露光(CP:Character Projection)方式を用いることで、「シャトルウェハで0.5wph程度」(同)まで引き上げることができたが、それでも研究開発領域での適用にとどまるのが実情であったという。

DEFBは、RTL(論理設計)後の回路合成段階より、EB直描を前提としたセルライブラリの工夫といった最適設計手法を取り入れることで、VSB方式のみの時と比べ、(CP方式と組み合わせることで)約10~25分の1にショット数を圧縮しスループットを向上させようというもの。

|

|

|

D2S)のChairman兼CEOであるAki Fujimura(藤村晶)氏 |

CP方式については、「65nmプロセス以降の世代では、より複雑なパターンが(ステンシル内の)キャラクタに収まるようになる。これにより例えばSRAMコアセルでは、3×3アレイが一括描画できるようになり、VSB方式と比べ1/144にショット数を圧縮することができるようになる」(D2S)のChairman兼CEOであるAki Fujimura氏)という。

土川氏は、「シングルビームのVSB方式に比べ5~10倍の処理能力向上を目指したい」としており、2009年度以降にはLSIの試作サービスを開始することを目指す。また、将来的には「MCC(マルチコラムセル)技術を採用することで、さらにスループットを向上させ、量産への適用も図りたい」(同)とした。

同合意に先立ち、3社はFMLの65nm LPプロセスを採用したテストチップを作成している。7層のメタル配線にEB直描が用いられており、ランダムロジック規模は300万ゲート以上、チップサイズは4.2mm×8.4mmとなっている。このチップの物理設計はD2Sが担当し、製造はイー・シャトルが担当した。3社では、このチップの評価を2008年度中に終えるとしている。

また、40nmプロセス世代の配線VIA層向け技術を開発しており、こちらは2009年の第1四半期に導入される予定としているほか、トランジスタ層へのEB適用も検討を進めており、これが実現されると、全領域にわたりEB直描が可能となるため、従来のマスク作成からチップ製造といった手番の短縮ができるようになる。

なお、イー・シャトルでは、社外のカスタマ向けにシャトルの運用体制の確立を進めていくほか、欧米のシャトル扱い組織などと交渉を行うことで、広くカスタマに活用してもらえるように活動をしていくとしている。