AMDの「FirePro S9300 x2 GPU」やNVIDIAの「P100 GPU」のように複数チップをシリコンインタポーザに載せて相互接続した製品が出てきているが、コストが高いのが難点である。このため、半導体各社は、複数チップを搭載する、より安価で、高密度な配線ができるパッケージ技術の開発を進めている。

TSMCは「InFO-WLP(Integrated Fan-Out Wafer-Level-Package)」という技術を開発しており、Hot Chips 28において、InFO-WLP実装されたチップ間を接続する「LIPINCON(Low-voltage-In-Package-INtegrated-CONnect)」という技術を発表した。

|

|

低電圧信号インタコネクト「LIPINCON」について発表するTSMCのMu-Shan Lin氏 |

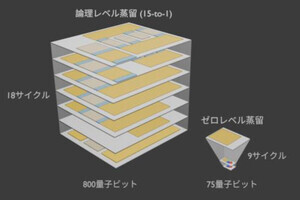

パッケージ技術は、多ピン化から複数チップ搭載へと動いており、多種の技術が開発されている。その中で。FO-WLPを選んだのは、「RDL(Re-Distribution Layer:チップの高密度の端子からパッケージまで配線する層)」の配線密度が高い(配線幅と間隔が5μm/5μm)、プリント基板接続のBGA(Ball Grid Array)を含めても約0.6mmという薄さ、TSVを作る必要が無いのでチップを小さくできるからである。

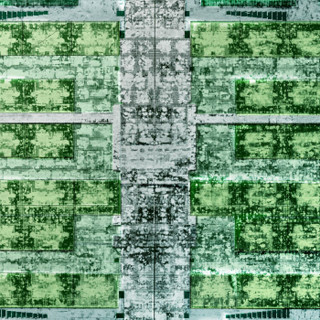

TSMCは、シリコンダイの間をモールド材で埋め、そこに配線層を作るInFo-WLPと呼ぶ技術を使っている。この技術は単一チップの場合でも、チップからの多数の高密度の信号線の間隔を広げてBGAのボールに繋ぐという使われ方もされている。

パッケージ上の配線は、チップ内配線より厚い銅配線が使えるので、抵抗値を小さくできる。また、低損失のモールド材を使うことにより、誘電体ロスを減らせる。そして、チップの背面はむき出しなので、熱抵抗が小さく、チップの温度を低く抑えられる。

InFOのチップを並べて、RDLの内層の配線で2つのチップの間の信号配線を行う。チップ間接続用のD2D BumpはI/Oのボールへの接続用のD2P Bumpより小さいBumpが使える。

BGAのボールを含めても0.56mmと薄く、装置を小型化できる。

2つのチップ間の配線は短いので、0.3Vという低振幅の信号が使える。また、終端抵抗を使わなくても良いので、消費電力も小さくて済む。

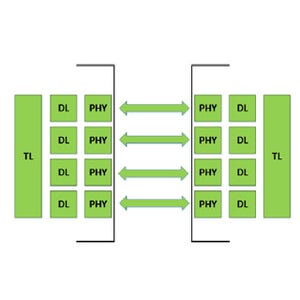

受信側は、クロックでゲートするセンスアンプを使う。この回路もスイッチする時だけ電力を消費する低消費電力の回路である。

信号配線が短いので、タイミングを合わせるPLLやDLLを不要にできる。PLLやDLLは比較的多くの電力を消費するので、これは省電力化にも貢献する。

次の図のように、D2D BumpはD2P Bumpの4倍程度の密度にできる。また、RDLの配線は、10μmに1本を通せる。これはプリント板の10倍以上の密度である。そして、隣接するチップ間の信号配線は550μmと短くできる。

D2D Bumpは小さく、プローブを接触させてチップのテストを行うことは難しい。このため、Boundary Scanを使ってテストする。各チップにはTAP(Test Access Port)コントローラを持たせる。TAPコントローラの制御信号などは、大きなサイズのD2P Bumpに接続されており、このバンプにはプローブを接触させてTAPコントローラを動かす。

そして、TAPコントローラ経由で、各ピンのオープン/ショートを試験する。

2つのチップのTAPコントローラを直列に繋ぎ、一方のチップから信号を送り、それが受信側のチップで正しく受け取られたかをテストし、信号配線を試験する。この方法で、ピンごとに故障の有無を検出できる。このように、TAPコントローラとバウンダリスキャンセルを使えば、D2D Bumpをプローブしないでも、チップのI/Oやチップ間の配線の試験を行うことができる。

256本のDQ信号線が同時にスイッチするので、大きなノイズが発生して信号線に載ってしまう。このノイズを小さく抑えるという点で、0.3Vと信号振幅を小さくすることは非常に重要であるという。

次の図は256DQ信号での疑似ランダム信号を伝送させた場合のアイをプロットしたものであるが、アイの幅は420psでこれは0.84UIに相当する。また、電圧的にはアイは225mVと信号振幅の75%もある。

|

|

256DQ信号の伝送アイパターン。アイの高さは225mV、アイの幅は0.84UIと非常に大きなアイが開いている。伝送する信号は疑似ランダム信号で、ノイズを減らすためデータバス反転(DBI)を使っている |

シミュレーションで求めた、1ピンのI/Oがフルにスイッチした場合の消費電力を次の表に示す。LIPINCON回路の制御部(DCDL)の消費電力は31.52mWで、1ビットの伝送に必要なエネルギーは0.062pJ/bitとなる。信号のドライバなどを含んだPHY全体の消費電力は217.141mWで、0.424pJ/bitのエネルギー効率となっている。

結論であるが、InFOパッケージを用いたメモリチップ接続を実証した。使用テクノロジはTSMCの16FFとInFOの組み合わせである。256DQの伝送路を2.8Gbit/sの速度で動かし、89.6GB/sのバンド幅を得た。信号伝送に必要なエネルギーは0.424pJ/bitと小さい。また、メモリのWriteは6.25T、Readは3.875Tという短いレーテンシが得られた。

0.3V振幅の伝送路の特性をプローブを接触させることなしに測定し、アイの幅は420ps(0.84UI)、高さは225mV(75%)であることを明らかにした。