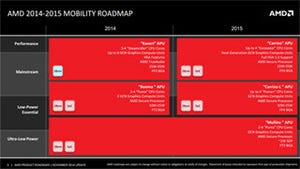

米AMDは23日(現地時間)、米国・サンフランシスコで開催されているISSCCにおいて、同社の次世代SoC「Carrizo」(開発コード名)の詳細を明らかにした。これに先立ち電話会議の形で説明会が行われたので、その内容をまとめてお届けしたい(Photo01)。ちなみにISSCC(nternational Solid-State Circuits Conference:国際半導体回路会議)という名前からもわかる通り、今回の発表内容はCarrizoで利用された回路技術がメインであり、製品のロードマップなどは出てこないことをあらかじめお断りしておく。

「Carrizo」の概要をおさらい

Photo02がCarrizoの概略である。新開発のCPUコア「Excavator」に、DirectX 12対応のGPUコア、それにARM TrustZone対応のSecure Processorを統合した構成である。またこのスライドには無いが、製造プロセスは28nm(Foundaryは後の質問でも非公開とされたが、おそらく引き続きGlobalFoundriesであろう)である。また、「Carrizo」ファミリとしては、CPUコアに「Puma+」を採用した「Carrizo-L」もラインナップされる。

このあたりの情報については2014年11月にお伝えした通りだが、このときの説明ではCarrizoとCarrizo-Lが完全に同じインフラで動作することを強調していた。チップセットを内蔵するという時点でVRM(Voltage Regulator Module:電圧レギュレータモジュール)以外の仕様は当然同じになるし、VRMの仕様も事実上フォームファクタで決まる。このことからもインフラは同じとして差し支えはないだろう。

ただ、CarrizoとCarrizo-Lが同じインフラを使うとなると、メモリはCarrizoとCarrizo-Lともにシングルチャネルなのか、あるいはデュアルチャンネルをサポートするのか、それとも信号ピンは2ch分用意するが、Carrizo-Lでは1ch分のみを有効とするのかなど疑問が出てくるが、この情報だけでは判断できない。

高密度で低消費電力な設計を採用

さて、ここからが今回の具体的な発表内容である。CarrizoはMobile向けに15~35Wという低いTDPの枠で動作する関係で、絶対性能ではなく性能/消費電力比を向上させることがメインテーマのProcessorだ。AMDはこのテーマに向けて、CarrizoでLibraryを従来のHP(High Performance)からHD(High Density)に切り替えた(Photo03)。

Libraryとは何か? を簡単に説明しておけば、半導体回路の設計において良く利用される回路をまとめてものだ。一般的にはCell LibraryとかStandard Libraryなどと呼ばれるが、これは基本的にFoundaryが提供する。

Photo04は、ARMが自社のCortex-AプロセッサをFinFETで実装する際にどんな選択肢があるのか説明した際の概略である。左にあるのがStandard Cellのバリエーション、右がそのバリエーションごとの性能特性である。グラフはTrack数(図でいえばStandard Cellの高さにあたる)と動作電圧(LVT/HVT/RVT)でどう特性が変わるかをおおざっぱに示したものである。ここで議論に関係するのはTrack数である。

|

Photo04:実はこの図は、20nmのStandard Cellが14nmになるとどう変化するか、という説明の中で「変化した後」のみが示されている。そのためこれだけ見てもちょっと分かりにくいかと思う。出典は2012年のARM Tech Symposium TokyoにおけるARMのVikas Chandra氏による"Design and 14nm"というスライド |

Photo04の左側では、Standard Cellの縦横に配線が交差しているわけだが、高さ(Track数)というのは要するに横方向の配線が何本入るかにあたる。グラフでは12T(12 Track)と9T(9 Track)での比較となっている。昔は16Tとかあったが、最近の先端プロセスでは12Tもだんだん使われなくなり、現在では10.5T/9T/7.5Tあたりが主流になってきている。

さて、Track数が多いほど、1つのStandard Cellに多くの機能を持たせることができる。これによって、Pipeline 1段あたりのStandard Cell数を減らせるので、結果として高速動作に有利となる。ただし多くの機能を持たせられるというのはその分無駄が出るということでもあり、エリアサイズはむしろ増える方向にある。

逆にTrack数を減らすと、機能も減らさざるを得ないから、Pipeline 1段あたりのCell数が増えることになり、高速動作には不向きとなる。しかし、Cellそのものの無駄な機能が減り、エリアサイズの節約になる。

従って、CPUなどの動作速度が速い回路には12Tなどの大きめのStandard Cellを、GPUなどの速度はやや低いものの回路規模が大きなものには9Tあるいは7.5Tといった高密度なStandard Cellを利用するのが一般的な考え方になる。Photo03でいうとTrack数の多いStandard CellのLibraryがHigh Performance Libraryで、少ないStandard CellのLibraryがHigh Density Libraryにあたる。

話を戻すと、Kaveri世代まではCPUにHP Libraryを採用していたが、CarrizoではこれをHD Libraryに切り替えた。その結果、FPUやFMACなどは、Kaveriと比較して30%以上面積を削減できたとする。実際にプロセッサ部のダイ写真を比較するとこれは明白である。

また、ある閾値(Photo03の場合、2コアで20Wを閾値としている)で同じ動作周波数になるようにKaveriとCarrizo(というか、SteamrollerとExcavator)を設計した場合、その閾値より下では性能/消費電力値が最大23%改善しているとする。動作周波数が低ければ、エリアサイズの縮小はそのまま配線の長さを短縮することにつながる。これは配線抵抗による消費電力低減になるし、その分コア電圧も落とせるから消費電力を低減する効果もあるというわけだ。

Photo05の左のグラフは、どんな特性のトランジスタを利用したかの比率である。縦軸のIoffはトランジスタがOffの場合の電流(要するにリーク電流)の多さで、横軸のIonはトランジスタがOnの場合の電流値となっている。CarrizoではKaveriと比べてIon電流が多少減ってもIoff電流を下げる、つまりリーク電流を減らす方向にトランジスタをシフトさせている。

|

左のグラフは、オレンジがKaveri、青がCarrizoと理解すればよいと思う。ちなみに(Photo04にも出てきたが)右の説明にあるRVTはRegular Voltage Thresholdで、正規の閾値電圧である。高速化にはVtを引き下げる事が必要だが、CarrizoではVtをむしろ引き上げることで消費電力削減を実現した |

また、CPUとGPUを統合したAPUでは、CPUをHP Library、GPUをHD Libraryで分けて作るというのは設計ツール側の問題で不可能だった。そのため、これまではGPUもCPUと同じくHP Libraryで構成されていた。ところがCarrizoではCPUにHD Libraryを使うことで、GPUもHD Libraryを利用することが可能となり、結果として最大で20%の消費電力削減が可能になったとしている。

電圧管理機能を強化

Carrizoで、新しく追加された機能としてVoltage Adaptive Operationも紹介された(Photo06)。これは何か? というと、供給電圧が高い場合に、一瞬動作周波数を下げて供給電圧を正規に戻すという仕組みである。

|

Photo06:オンダイVRMとまではいかなくてもオンチップVRMが利用できればこのあたりはずいぶん改善されるが、これが搭載されるのはCarrizoの次の世代になりそうで、Project SkyBridgeでも間に合うかどうか |

一般論として、マザーボード上に搭載されたVRMは、電圧を規定よりも若干(10%程度)高めに供給する傾向がある。電圧で10%増しなら電力では20%増しになり消費電力の増加につながる。これを抑えるために、CarrizoではCPU内部に精密な電圧センサを搭載し、一定時間以上基準値より高い電圧供給が続いたら、一瞬だけ動作周波数を落とす動作をとる。

昨今のVRMは動作周波数に応じて電圧を可変する仕組みがあるから、これによって周波数が一瞬下がると、それに伴い電圧も下がり、そこから正規の電圧に復帰することになる。これによって、CPUが最大19%、GPUも最大10%の消費電力節約が可能になるとしている。

また、2つのExcavator Moduleに対して合計で10のAVFS(Active Voltage Frequency Scaling)モジュールが搭載され、合計で500カ所で動作周波数の測定を行うほか、AVFSモジュールが測定したデータによってCPUの動作を最適化しているという。AMDはこのVoltage Adaptive Operationと、先に述べたHD Libraryの併用により、動作時の大幅な消費電力削減が可能になったと説明する。

S0i3ステートを追加

さて、これに加えてCarrizoではS0i3ステートの実装も行われた(Photo08)。BoostあるいはActive Sustainedというのは稼働中であり、Carrizoの場合であれば製品のTDPは15~35Wとされる。この時には内部の全コンポーネントが稼働する。

ここでIdleになると、CPU CoreとGraphicsがPower Gatingにより電源供給が止まる。ただしその他の周辺回路は引き続き保持されているし、CPU/GPU向けのPLL(クロック生成)はとまっているが、周辺回路向けはまだ稼働している。

AMDによれば、この状態での消費電力おおむね1.5W未満である。S0i3では、ここからさらにI/OのほとんどとNorthbridge機能、PLLも落とすもので、この段階では50mW未満の消費電力まで削減されるという。

ACP/FCHとI/Oの一部が残るのは、どこかに「再び起動する」ための回路を残しておかないと、電源スイッチを入れ直さない立ち上がらなくなってしまうためで、PCでいえばキーボード/マウスが繋がるUSBコントローラ、あるいはMobile向けのConnected Standbyならモデムからの割り込み要求を受ける部分だけは残しておく必要があるためである。ちなみにS0i3からS0への復帰時間は数msのオーダーだとのことである。

絶対性能は向上はどの程度か?

次のスライド(Photo09)は2014年のAMD Future of Computing 2014でも公開されたものだが、左のEnergy Efficiencyのグラフは初出であって、CarrizoはKaveriの2倍近い性能/消費電力比を実現するとしている。

では絶対性能は? ということで最後にちょっとだけ出て触れられた(Photo10)。まずCPUコアは、IPCの改善は5%程度とされており、この面での改善はあまり期待できそうに無い。H.265に関しては、ハードウェアでDecoderを搭載しており、GPU側でEncodeを行うことで、トータルで3.5倍のTranscode性能としている。

GPUは、Kaveriが6つのCU(Compute Unit)で構成されたのに対し、Carrizoでは8つになることが明らかにされている。SP数でいえば512SPが最大構成ということだが、CUが6から8に増えたことで、単純に1.3倍の描画性能になるかどうかはメモリ帯域や動作周波数の関係もあるので、現時点ではなんとも言えないところだ。

以上がISSCCにおけるCarrizoに関する発表の詳細である。考察というか、実際の製品に関する話は、また別記事であらためてお届けしたい。