2つ目の製品がボイス制御MCUである(Photo09)。こちらはそのもので、複数の言語を認識するMCUである。具体的には100語以上の言葉をテキストファイルの形で定義して格納しておく(Photo10)と、それを認識して結果を返してくれる。もちろん用意されるのは音声の認識までなので、その先はアプリケーション次第ということになる。会場ではマイク入力でコマンドを認識すると、その結果をPCに送り、PCの側にリモコン機能を実装する形でTVを操作するデモが行われた(Photo11)。

Photo12が内部構成であるが、動作周波数は160MHzないし200MHzということでやや高速である。さて、肝となるのがCPUの中にある「ASR(Automatic Speech Regognition)」であるが、これはハードウェアではなくソフトウェアである。核になる技術は、同社が2012年に発表したAcoustic Coprocessorである。これはNuance Communicationsをベースにしたものだが、今回の技術もこの延長線上にある。ただし同社はあれから実装の最適化をずっと進めていった結果、Cortex-M4ベースのMCUの50%程度の処理負荷で同等の音声認識機能を実装できるようになった、という話だそうだ。ちなみに音声辞書は0.5MB程度で済んでおり、Acoustic Coprocessorの世代で必要とされた2MBから大幅に削減が出来ている。また50%の処理負荷に関しては、CPUコアだけでなくDSPユニットもフル活用しているとのことだ。逆にFPUは(内蔵はしているものの)音声認識では特に利用しないという話で、むしろ先にでたグラフィックMCUで映像処理にFPUが多用されるとの事だった。ちなみに環境ノイズの有無とかしゃべり方(特にイントネーションの違い)などには処理負荷はほとんど影響しないそうである。

面白いのはDual Flash Bankであるが、辞書が0.5MB程度なのでこれにプログラムを含めても1MBあれば十分である。最初は160/200MHz駆動に0waitで間に合わせるために、Interleave的な使い方をするのかと思ったのだが、確認したところそういう使い方はしない(Flash Accessは平均1~2waitが入るそうだ)との事。これはWi-Fiなどを経由したOver-the-Air Firmware Updateに対応したもので、片方のバンクをアクセスしながら、もう片方のバンクをUpdateし、完了したらそのままon-the-flyで切り替えといった事もできるとしている。またCodecが外付けとされたのは、とりあえず汎用的に利用してもらう(特定用途向けMCUではない)ために、あえてCodecは内蔵しなかったという話であるが、将来的に特定用途向けのニーズが強くなった場合は内蔵することもありえる、との話だった。

どちらの製品も現在はサンプル出荷中であり、1万個発注時の価格はグラフィック制御MCU(S6E2DHシリーズ)が5.05ドルから、ボイス制御MCU(S6E2CCxxFシリーズ/MB9BF568Fシリーズ)が6.95ドルからとされる。また開発キットとしてはFM4 Graphics MCU Starter Kit、FM4 Voice Command Starter Kitともに3月から提供予定とされる。

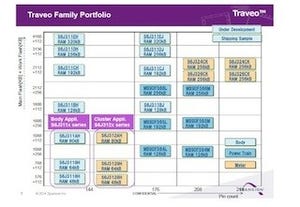

ついでにもう少し先の話も。同社はすでにCortex-M7のライセンスを受けており、すでにロードマップにも記載されている(Photo13)が、登場時期は「今年の後半にアナウンスを予定している」という話であった。

さて、今回の2製品は90nmプロセスでの製造となるが、既に同社は40nmのeCT(embedded Charge Trap)の技術をモノにしており、2013年末にはこれをUMCに提供する事を発表しているので、普通に考えればCortex-M7ベースのFM7はUMCの40nmプロセスを使っての製造となると思われ、Handa氏もこれを肯定した。実際、氏は今年中に40nmを利用した製品の製造が始まるとしている。90nm→40nmというのは結構大きなジャンプであり、普通は中間ノード(65nmあるいは55nm)を挟みそうなものだが、氏によれば自動車向けMCUは55nmを利用するものの、汎用品は直接40nmに以降するようだ。理由は明確には述べて下さらなかったが、55nmのEmbedded FlashはすでにMatureな技術であり、複数社がこれを利用してMCUの開発を手がけている(自動車向けでは結構なメーカーがすでに55nmプロセスを使った製品の出荷あるいはサンプリングを行っている)から、ここでの差別化は難しい。ところが40nmは今のところ利用できるFabが限られており(UMCはすでに可能とされるが、TSMCはまだ開発中)、なので先行者利益を得やすいというあたりにアドバンテージがあると想定しているのではないかと思われる。

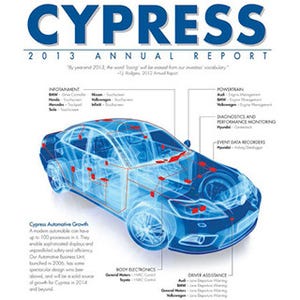

またCypressの製品との統合に関しては「今まさにやり始めたところで、まだ答えるには早すぎる」ということ。それでも「数カ月後には何らかのロードマップが発表できるかもしれない」との事であった。