Alteraは10月1日、「MAX10 FPGAファミリー」を正式に発表した。これに先立ち、都内でこのMAX10に関する説明会が行われたので、この内容をご紹介したい(Photo01,02)。

|

|

|

|

Photo01:最初に挨拶を行った日本アルテラ 代表取締役社長のハンス・チュアン氏 |

Photo02:MAX 10シリーズの説明を行ったPatric Dorsey氏(Senior Director of Product Marketing) |

そもそもAlteraは随分早くからMAX10に関する情報をアナウンスしていた。今年5月末にはMAX10のテープアウトに加え、Quartus IIのβ版提供と早期アクセスドキュメントの提供を開始している。そんな訳でMAX10という製品の情報そのものは随分前から知られていたわけだが、本日の発表は製品出荷、及び評価キットに関する情報がメインではある(Photo03)が、もう少し細かい情報も説明された。

MAX10の特徴は先の記事にもあるとおり、Embedded Flashをチップ側に搭載することで外部にConfiguration Flashが不要になったことであるが、ほかにも

- Dual Configuration

- Integrated analog Blocks

- DDR3 External Memory I/F

といった特徴を持つ製品である(Photo04)。

ただMAXシリーズはこれまで、低価格向けのCPLDに位置づけられており、これを継承してかMAX 10もパッケージはBGAないしPQFPのかなり小さなものに用意されている(Photo05)。

ただそうでありながらも、MAX 10では集積度を高めているのが特徴である。Dorsey氏は従来のCPLD/FPGAとMAX10を比較しながら、BOMと実装面積を大幅に抑えられる事を強調した(Photo06,07)

|

|

|

|

Photo06:FPGAにMCUとADCを組み合わせる場合の構成例。ほかにClockとか各種電圧レギュレータが必要になる |

Photo07:MAX 10ではこれらを全部統合可能であり、外部に電源管理用のEnpirionチップとClock1個あれば良いとする。電圧レギュレータそのものはMAX 10内部に搭載される |

もう少し詳細を見ると、まず内部構造がPhoto08である。最大50KのLogic Elementに加えRAM BlockとDSP Blockを実装している。これに加え、2つのConfiguration Flashと1つのUser Flash、12bit ADC×2、PLL×4、電源レギュレータ、さらには外部接続用のDDR3 I/Fも実装している。このあたりは旧来のMAXシリーズの延長線上にある感じだが、大きく異なるのはNios IIが動作すること。従来の同社のCPLDとFPGAの違いの1つが、Nios IIが動くか動かないかだった(MAXシリーズはNios IIが動作しなかった)。ところが今回MAX 10ではNios IIが動作することになり、(これだけが理由ではないにせよ)CPLDではなくFPGAという扱われ方をしている。

|

|

|

Photo08:ちなみにLUTの構造を尋ねたところ「4入力LUTで、Cyclone IIIまでのものとも互換性がある。ただそれはQuartus IIで再構成ができるという意味で、(Configurationの)bitstreamそのものに互換性はない」(Dorsey氏)との事だった |

特にMAX 10で特徴的なのはConfiguration Flashを2つ持つことだ。これにより、たとえばFlash 2にはバックアップ用のConfigurationを入れておき、もしFlash 1のUpdateに失敗した(とかFlash 1のConfigurationにバグがあったので入れなおしたいなど)場合には、Configuration 2から立ち上げなおしてリカバーが可能になる。これは特に、出荷後の製品をOn the flyでupdateするなんてケースでは得がたい特性である。また2つのFlashに別々のConfigurationを入れておき、切り替えるなんて事も不可能ではない。ただし切り替え時間は10msほど掛かるそうで、こうした使い方はあまり実用的ではないかもしれない。

話を戻すと、これによりMAX 10を立ち上げると、初期化後に内部のFlashからConfigurationを読み出して実行が始まるわけで、FPGAというよりはMCU的にな使い方が可能である。そのMCU的な使い方のキーになるのがNios IIであるが、こちらは従来同社が提供してきたものそのままである(Photo10)。

また今回、初めてADCが内蔵された(Photo11)。この目的は、MAX 10を使ってシステムを構築する際、システムとかチップの環境温度をそのままMAX 10で取り込んですぐに監視ができるようにという事が最初の目的らしい。ただ、それ以外の用途にももちろん利用できる。その一例としてDorsey氏は、ADCにマイクを接続して音量を計測し、それをLCDパネルに表示するというデモを実演した(Photo12)。

|

|

|

|

Photo11:少なくとも当面はADCのみで、たとえばコンパレータとかVoltage Reference、あるいは出力系アナログは統合しないという話であった |

Photo12:これはMAX 10の評価基盤にマイクを繋ぎ、その上にArduino ShieldのLCDパネルを載せたもの。USBは電源供給用らしい |

さて、ここからはこのMAX 10の適用分野について簡単に説明があった。Industrial(Photo13)、Automotive(Photo14)、Computation(Photo15)という代表的な3分野において、幅広く利用できるとしている。

|

|

|

|

|

Photo13:Roboticsに本気で使おうとすると、ADC×2で足りるのかはちょっと疑問 |

Photo14:ここまで色々ラインアップされているところを見ると、MAX 10にもAutomotive Gradeが用意されると思われる |

Photo15:最近はFPGAを使ったHPCも取りざたされているが、そうしたハイエンドの話ではなく、システムコントローラ的な使い方を想定している模様 |

実際、これまでCPLDではやや性能不足だった領域をMAX 10ではカバーしているから、幅広く利用できる事そのものは間違いない。ただその一方で、たとえばIndustrialとかAutomotiveではEthernetやらPCI Expressやらのニーズもあるわけだが、そうした事に対応する高速トランシーバは搭載していないとの事。「I/Oをフルに駆動すればPCI Busは構成できると思うが、PCI Expressとかはサポートしない。そうしたニーズはCyclone VあるいはArriaが適している」(Dorsey氏)との事だった。

さて、最初にも少し触れた話だが、10月1日の時点で、MAX 10のみならず開発ボードやQUARTUS II、ドキュメントやサンプルなどが一斉に公開される(Photo16)。

特筆すべきはその価格で、デモにも利用された開発ボードは49.95ドルという驚くべき低価格である。基板上にはArudino Shield互換のピンが用意されており、既存のShieldが利用できる事になる。

|

|

|

Photo17:ボードの開発そのものはEMSのaXelsysが担当した模様。このボードはAlteraから購入できるほか代理店経由でも購入可能になるらしいが、原稿執筆時点ではまだ詳細が決まっていないとの事だった。 |

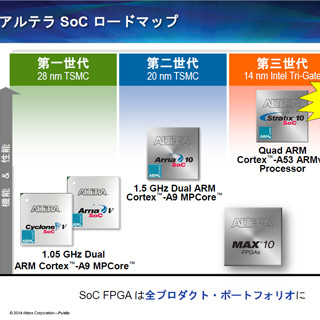

ということで、MAX 10の発表は以上であるが、最後にこんなスライドが示された(Photo18)事は、今後のラインアップを示唆しているように思う。それは、Cycloneの製品ラインの消滅である。今回発表されたMAX 10はMAXというCPLDのシリーズ名を使いながら、実態はFPGAレベルに拡張されている。おまけにCyclone IIIまでと構造に互換性があるわけで、つまりCLPD~Cyclone IIIまでの規模の開発をこのMAX 10で代替する形を狙っているように思われる。ではCyclone IVとかCyclone Vは? というと、Arriaに吸収される方向を考えている様に思われる。もともとCycloneとArriaの違いはハイスピードトランシーバの搭載の有無だった筈なのに、Cycline IV以降はこれが崩れており、Arriaとの違いは規模だけになっている。これを10世代では整理し、既存のCycloneのマーケットを2つに分割、下側はMAX 10で、上側をArria 10で吸収する形を考えている様に思われる(Photo19)。

|

|

|

|

Photo18:ここにCycloneが無い、という時点でCycloneの製品ラインの存続がかなり怪しい気がする |

Photo19:MAX 10に比べると、かなり巨大というイメージがある。これはDorsey氏が「丁度持ってるから」ということで展示されたサンプル |

こうした構図は、分割の仕方はちょっと違うがXilinxのSpartanがArtixとKintexに分割されて消えた事を連想する。ある意味、MAX 10はXilinxのArtix迎撃のために機能と性能を充実させた、という感じが非常に強いと筆者は感じた。

最後にちょっとだけ余談を。MAX 10はTSMCの55nm Flash混載プロセスだが、原理的にこのプロセスは他のアナログ部品も実装しやすい。ということは長期的にはMicrosemiのSmartFusion 2の様にアナログを充実させる方向性も可能である。このあたりをDorsey氏に確認したところ、その可能性はある、という返事だった。このあたりはXilinxとの戦略の違いで、XilinxがTop to bottomで同じプロセスを利用するのに対し、Alteraは製品ごとに最適なプロセスを利用する。であれば、アナログ回路を充実させるのは差別化の目的に適っている事になる。このあたりが今後どうなるか、が楽しみである。