Hot Chips 26において、MicrosoftはFPGAを使って、再構成可能なコンピューティングを行うデータセンターサーバについての発表を行った。

巨大データセンターでは、費用対性能、消費電力対性能が重要であり、サーバのコスト効率や電力効率の改善の追求が続けられている。CPUによる処理よりも専用ロジックによる処理の方が効率は高いのであるが、専用ロジックを使おうという試みは、これまで成功して来なかった。

それは、データセンターのソフトウェアは毎月変更が入り、マシン自体の寿命も3年程度と短く、かつ、その半分くらいの期間で、別の用途に回されるという使い方がされるので、固定機能のアクセラレータでは直ぐに使えなくなってしまう。また、データセンター全体の機器は、できるだけ同じものを使う方が、保守や使いまわしの点で有利なので、特定用途に専用の機器を導入するというのは望ましくない。

そこで、FPGAで機能を可変できるアクセラレータを考えるのであるが、FPGAアクセラレータの入れ方には、次のように3つの方法が考えられる。

|

|

FPGAの付け方としては、FPGAアクセラレータだけのラックを付けるという集中型から、ラックごとにFPGAアクセラレータをまとめて付ける、個々のサーバにFPGAを付けるという色々な粒度が考えられる。(出典:この記事のすべての図は、Hot Chips 26でのPutnam氏の発表スライドの抜粋である) |

FPGAアクセラレータ付きのサーバを、ラック単位やラック内にある程度まとめて設置する方が、一般のサーバに影響を与えず導入が容易と考えて、6個のFPGAを搭載したPCIeボードを作ってGPUの代わりにサーバに搭載したのであるが、不均一なノードが混在するので、ラックの熱設計などが複雑になる、保守性も悪い。また、FPGAを使おうとすると、ネットワークを経由して使うことになるので、レーテンシが重要なアプリケーションには使えない。さらに、6個のFPGAでは規模が不足な用途には使えないという問題などがあり、具合が悪かったという。

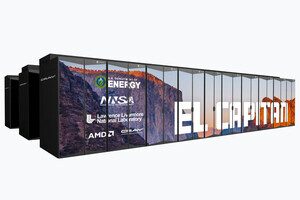

そこで、次の図に示すように、FPGA同士の通信ができ、規模を可変できる。また、サーバとしては全て同じものが使える解であることが基本要件で、加えて、サーバのコスト上昇は30%以下であること。消費電力の増加は10%以下で、PCIeコネクタから供給できる25W以下であること。また、現状のサーバとしての動作には影響がなく、ネットワークの変更も必要なく、故障率も増加させないことを要件として、設計を行ったという。

マイクロソフトのOpen Computeサーバは、次の図のような1Uで半分の幅のブレードであり、1/2高さ、1/2幅のPCIeカードは追加できるが、GPUを入れるほどのスペースや電源の余裕はない。

この1/2高さ、1/2幅のPCIeカードに中規模のFPGA 1個と8GBのDIMMを1枚搭載するCatapultと呼ぶカードを開発した。そして、x8のPCIe3.0コネクタでマザーボードに接続する。

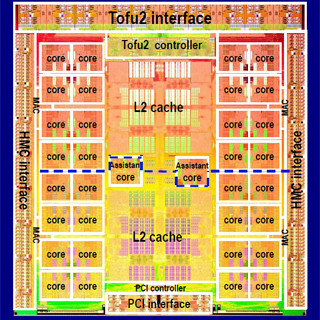

そして、FPGAのロジックと高速IOを使って、2次元トーラスを構成するスイッチを内蔵させている。リンクのバンド幅は20Gbit/s、ホップあたりのレーテンシは400nsである。この回路を使って、ラック1/2本分の48ノードのCatapultカードを6×8の2次元トーラスとなるように接続している。

8枚のカードを接続するケーブルと6枚のカードを接続するケーブルを作り、これを使って6×8のトーラスを構成する。なお、これらのケーブルを抜くことなく、ブレードサーバの交換は可能になっているという。