CoprocessorのMICとアクセラレータのGPU

米テキサス大学TACC(Texas Advanced Computing Center)のスーパーコンピュータ(スパコン)「Stampede」はIntelのXeon E5 CPUとMIC(Many Integrated Core)アーキテクチャを採用した「Xeon Phi SE10P」を使うハイブリッドスパコンである。第40回のTop500リストの中には、IntelのXeon Phiをアクセラレータとして使っているシステムが7システムある。しかし、NVIDIAのKepler GPUを使うシステムは50システムあり、 Stampedeを広告塔として、この情勢を挽回していこうというところであろう。

IntelのメニーコアのXeon Phiであるが、IntelはCoprocessorと呼んでいる。一方、GPUはアクセラレータと呼び、両者にはかなり違いがあるとしている。

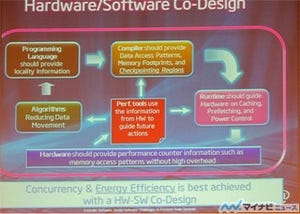

まず、アーキテクチャについては、MICはx86アーキテクチャであるのに対して、アクセラレータはStreaming Processorである。そして、MICは全コアでコヒーレントなキャッシュを持っているが、GPUはシェアードメモリでコヒーレンシが無い。そのため、MICはC++/C/FortranでOpenMPを使ってスレッド並列のプログラムを作れるのに対して、GPUはCUDAやOpenCLというGPU向きの言語でプログラムする必要がある。

MPI並列に関しても、MICは自分自身のコアでもホストCPUでもMPIノードとなって通信が出来るが、GPUはホストCPUを使わないとMPI通信ができない。

どちらも計算量の多い部分をオフロードするエンジンであるが、MICの場合はホストCPUと同じx86であるので、単純にプログラムの1部を切り出せばよいが、GPUの場合はKernelをCUDAなどでプログラムする必要がある。

ということで、x86アーキのMICの方がどのようなプログラムでもオフロードできるというメリットがあるとする。

既存のx86プログラムを性能を気にせず、単にMICで動かすだけなら非常に簡単であるが、MICには大量のGDDRメモリが付いており、また、100+のスレッドを走らせるプロセサコアがあるので、これらを有効に使用するためには工夫が必要である。

MICには6GBのGDDR5メモリがついているが、走らせるスレッドも100+と多いので1つのスレッドが利用できるメモリはそれほど大きくない。MICのコアごとにMPIタスクを走らせるとMPIのバッファだけでも数10MBを必要とし、コアごとにMPIというのは良い方法ではない。コア間はOpenMPなどでスレッド並列にするのが良い方法であるという。

まあ、これは当然で、京コンピュータでもチップ内のコアはOpenMPで並列化し、チップ(=ノード)間をMPI並列としている。しかし、このようにすると、結局、ホストCPUでMPIを走らせることになり、最初の比較で述べたMICのコアでMPIが動かせるというメリットは活かせなくなる。

Stampedeスパコンの構成

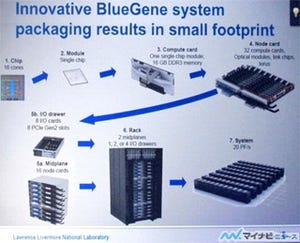

StampedeはNational Science Foundationの資金で作られる、すべての科学、技術分野のオープンなサイエンスをサポートするスパコンであり、その概要は次の図のようになっている。

今回のTop500ではXeon Phiは112,500コアとなっており、まだ、1800個あまりの台数しか組み込まれていないが、2013年1月7日の正式稼働時には6400台以上のXeon Phiが搭載される計画になっている。結果として、CPU部分で2+PFlops、Xeon Phi部分で7+PFlopsとなり、全体では、約10PFlopsのピーク演算性能をもつことになる。そして、メインメモリは272TB以上、ディスクは14PB以上となる。また、計算ノード群とは別に、NVIDIAのK20 GPU 128台を使う可視化用のクラスタも設置される。

Stampede全体では筐体が182本で、8000ft2(約800m2)の面積を占め、消費電力は6MWとなる。

計算ノードはDellのPowerEdge C8220ブレードで、8コアのXeon E5-2680を2個搭載している。そして、もう1つのブレードがペアになっており、こちらにXeon Phiを搭載する。このブレードには最大2台(写真では、左側に裏返しに搭載されたXeon Phiがあり、右側は空きとなっている)のXeon Phiを搭載するスペースがあり、一部のノードには2台目のXeon Phiを追加するので、Xeon Phiの台数は6400台以上となる予定である。

StampedeのインタコネクトはFDRのInfinibandで、Mellanox製の8台の648ポートのコアスイッチと330台の36ポートのリーフスイッチで接続されている。リーフスイッチとノードの接続は電気、リーフスイッチとコアスイッチ間は光ケーブルで接続され、総延長は約75マイル(120km)となっている。

なおStampedeシステムは、現在でもフレンドリーなユーザは使用を始めており、12月からは一部ユーザの受け入れを行う。そして1月7日から正式稼働の予定である。

もちろん、一部のユーザはXeon Phiを有効利用して10PFlopsのヘテロジニアスなハイブリッドスパコンとして使用すると見られるが、多くのユーザは、当初はMICを使わず、単に2+PFlopsのXeon E5システムとしてStampedeを使うと予想され、現状ではシステムの課金はCPUコア数単位とし、MICは無料という方針であるという。