今後の進め方とタイムテーブル

今回のアプリケーション作業部会では、アプリケーションの特性に基づく4種のアーキテクチャを提案している。汎用アーキ型は「京」の発展形、容量・帯域アーキ型はNECの提案するベクトルの発展形であるが、演算重視とメモリ削減アーキ型のイメージとして、牧野教授は、おおざっぱには1970年~80年代の大規模SIMDマシンを1チップ化したようなもので、コア内部アーキテクチャ、コア間の接続、チップ間の接続を考える必要があると述べた。

そしてコアの内部アーキテクチャの例として、牧野教授が開発を行ったGRAPE-DRのコアアーキテクチャを示した。

今後の進め方であるが、2011年度の2つの作業部会の報告を受け、ExaScaleのシステムの実現可能性を検討するFeasibility Study(FS)を行うことが決まり、検討チームの公募が行われた。その結果、アプリケーションに関しては理研と東工大の連合のチームが選ばれ、システムに関しては、容量・帯域アーキ型を検討する東北大とNECのチーム、メモリ削減と演算重視アーキ型を検討する筑波大、東工大と日立のチーム、汎用アーキ型を検討する東大と九大、富士通、日立、NECのチームの計3チームが選ばれた。

このFSには4億円あまりの予算が予定され、2012年度、2013年度の2年間でそれぞれのテーマの実現可能性(フィージビリティ)を検討する。

そして、石川教授は、自身が率いる汎用アーキチームの構成と担務として次の図を示した。

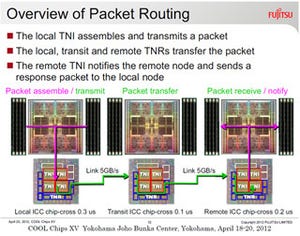

この図によると、アーキテクチャとしては京の発展形の次世代汎用アーキのスパコンと並んで、コモディティベースのクラスタ型のスパコンも検討範囲に入っている。そして、京の発展形の汎用スパコンについては富士通の新庄氏がハード、ソフトの検討を担当し、システムソフトウェアなどは石川教授、アーキテクチャの評価などは東大の平木教授、ネットワーク関係の評価は九大の青柳教授が担当することになっている。また、日立はストレージアーキテクチャ、NECはコモディティクラスタ型スパコンのシステムソフトを検討するようである。

そして、2013年度末に、これらのFSの結果を見てExaFlopsシステムの開発を行うプロジェクトを立ち上げるかどうかを判断することになる。そして、Goの場合は、3年間の開発期間と2年間の製造期間を見込んで5年後の2018年にハードとOSなどの基本ソフトや運用ソフトの開発を終え、2年間の運用で2020年度末には予定された科学技術的成果を挙げるというシナリオである。

ただし、米国では20MWでの1EFlopsの達成は2018年には無理という見方が多く、目標を数年遅らせるという話が出ており、日本の計画もこの通りに進むかどうかはFSの結果に掛っている。

なお、この石川教授と牧野教授のSS研での発表資料は公開されており、SS研のWebページからダウンロードすることができる。