はじめに

次世代通信となる第4世代(4G)やLTE(Long-Term Evolution)またはWiMax無線基地局の無線カードについては、クロックツリーによって対処する必要がある問題が多数あります。OFDM(直交波周波数分割多重)プロトコル自体による制約に加えて、A/Dコンバータ(ADC)、D/Aコンバータ(DAC)、およびRFミキサには、エイリアシングやフィルタリングに関する大きな課題があります。本レポートでは、変調エレメントに関する課題と対策について記載します。

ネットワーク構築とアップグレードの簡素化

ネットワーク構築とアップグレードの簡素化およびコスト削減を図るために、OEMベンダは、ソフトウェアの再構成をサポートし、また類似する複数の設計での再利用が可能な無線カード・コンポーネントが必要になります。

リモート・ラジオヘッドで無線カードが必要になる場合があるため、ほとんどの無線カードは基地局のリンクからリカバリされる単一の入力クロックを想定して設計されています。これら単一の入力クロックは低品質である可能性があり、無線カード上で他のクロックを適切に生成するには大幅なジッタ・クリーニングが必要になる場合があります。

このことから、無線カード・クロックツリーの中核になるのが、出力周波数のプログラムが可能なジッタ・アッテネータです。ここでは、ジッタ・アッテネータのパフォーマンス特性とその必要性、さらにその他のクロックツリー要件について説明します。

無線カードのアーキテクチャについて考慮すべき事項

現在の基地局における無線カード設計では、LTEやマルチキャリアGSMなどのプロトコルに対する信号の変換に必要な操作の多くが、デジタルで実行されるようになっています。エラー補正、チャネル・マッピング、あるいはI&Qストリームの分割は、デジタル方式の方が、処理が容易であるためです。

また、この混合信号の複雑なデータストリームでは、送信と受信の両方向で、非常に慎重にフィルタリング/信号処理を実行する必要があります。これをデジタル方式で実行すれば、高精度なマッチングが必要になるコンポーネントのコストを削減することが可能になります。

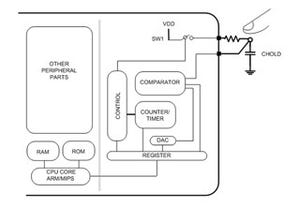

ただし、デジタル操作が広範に採用されている中でも、いくつかのポイントで信号を824MHz~2.62GHzの範囲の周波数に変調し、アナログ信号として伝送する必要があります。LTE、WiMax、マルチキャリアGSMなどのマルチチャネル・プロトコルに対応する多くの基地局のアーキテクチャでは、図1に示すように、一段階のアナログ変換アプローチが使用されています。

送信側では、個々の副搬送波が変調されずに、デジタル処理で単一のストリームに混合されます。このベースバンド信号はDACによって位相補正アナログI&Qストリームに変換され、直交位相アナログ・ミキサを通じて伝送周波数にアップコンバートされます。その間に可変/固定ゲインアンプとデュプレックス・フィルタが使用されることで、目的の信号が伝送帯域で求められる強度に引き上げられます。その間に加わるノイズや歪みはわずかであり、同時に伝送帯域外のエネルギーも最小になり、他のRFチャネルに対する干渉も防止されます。

受信側では通常、RF信号が増幅およびフィルタリングされ、ミキサを通じて75MHz~250MHz範囲の中間周波数(IF)に変換されます。この信号はさらに可変量で増幅され、フィルタリングされて、最後にナイキスト基準に従ってパイプラインADCによってサンプリングされます。それによって、副搬送波のダウンコンバートと復調がデジタル方式で処理されます。受信側では、ADCの処理能力を超えないようノイズと相互変調歪みの増可を最小限にし、ADCより前にシグナル・コンディショニングを実行することが目標になります。

無線カードの設計者は、クロックツリーが可能な限り統合されていることが望ましいと考えます。それは前述の理由からだけでなく、それぞれのクロックツリー・コンポーネントには個別にジッタを持ち、それによってクロック信号が規格外になる可能性があるためです。このような統合では、変調のためのRFおよびIFクロックだけでなく、ADCおよびDACのためのサンプリング・クロック、さらにCPU、ASIC、FPGAなどその他のデジタル・コンポーネントのためのクロックを発生させる必要があります。

通常これらのデジタル・コンポーネントのクロックは、RF信号パス関連のクロックと比べて仕様が非常に緩く、ほとんどの場合、周期ジッタが主な課題となります。これらのクロックをより高精度のクロックとして同じチップ上で発生させる場合には、2つの課題があります。第1に、デジタル・クロックが無線カードに対する入力クロック信号の整数倍になることは稀であり、フラクショナル・フィードバックまたはフラクショナル・出力・デバイダ技法を使用して生成する必要があることです。ただし、これらの技法ではいずれも、クロック・チップ内およびクロック出力に多量のスプリアス・コンテンツが発生します。第2に、RF、IFまたはサンプリング周波数に近接するデジタルチップ・クロック(またはクロックの発生中に生成されたスプリアス)は、フィルタリングによる除去が容易でないため避けなければなりません。そのような周波数以外のコンポーネントであっても、広帯域ノイズが発生すること、またはフィルタリングされていない場合に重要な周波数範囲でエイリアシングが発生することで、SN比を低下させる可能性があります。