ベルギーimecはパリ第11大学(Université de Paris-Sub)と共同で、スピン波の干渉を活用した多数決ゲートの動作に成功したことを発表した。また、これら2者にさらにIntelを加えた3者により、磁壁の伝播を用いてゲートを動作させることにも成功したことも明らかにした。

imecとParis-Sub大の研究は、スピントロニクスを活用した高効率回路の実現に向けたもので、スピン波の干渉を用いて、多数決ゲートで構成されたロジックの動作を行ったというもの。これまで、大きなスケール則でのデバイスを用いた報告はあったが、今回は、サブμmクラスでの多数決ゲートの動作に成功したとする。また、研究チームでは、多数決論理関数の真理値表の検証なども行なったとしており、ニューロモルフィックアプリケーションの実現の可能性が示されたとしている。

-

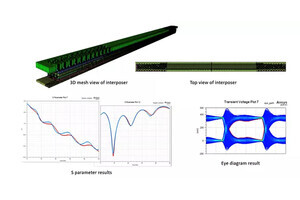

スピン波の干渉に基づく多数決ゲートデバイスの模式図(左)とSEM像(右)。SEM像に黄色い矢印で示された領域はスピン波の干渉が起きる強磁性スピン波バス(ferromagnetic spin wave bus) (出所:imec)

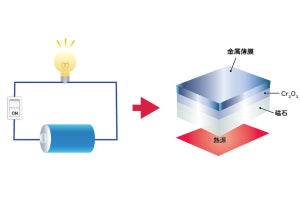

Intelを加えた3者の研究は、強磁性体の自由層に接続された磁気トンネル接合(MTJ)を有する磁壁の核生成、伝播および検出などをスピン伝達トルクやトンネル磁気抵抗を活用することで測定し、論理ゲートとして機能させることに成功したというもの。CMOS互換プロセスで300mmウェハ上に製造したとしており、従来の製造プロセスとの親和性が高いとimecでは説明している。