ベルギーimecと仏Soitecは、300mmウェハ上に2つの異なるデバイス層を低温で連続的に積層する3次元フロントエンド積層プロセスを開発したと発表した。

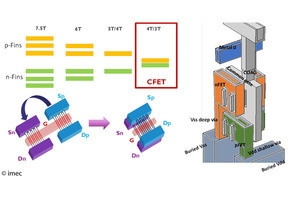

限界が見えてきたプロセスの微細化に代わり、デバイスを積層することで集積度を向上させることを目指した研究によるもので、imecなどは、「sequential-3D integration(S3D)」と呼ぶシリコン基板上にデバイス層を連続して積層する技術を用いることで実現したと説明している。

-

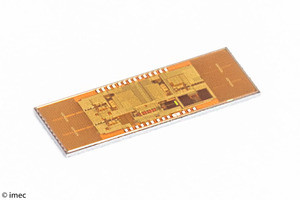

3次元積層構造のTEM断面写真。左がトップデバイスとボトムデバイスがナノレベルの正確なアラインメントで積層されている様子。中央がボトムデバイスへの3次元コンタクト、右がトップデバイスの拡大写真で上からNMOSおよびPMOS (出所:imec)

S3Dを実現するうえで、もっとも重要な課題は、製造時の熱バジェットの管理で、ボトム(下層)デバイス層の熱による劣化の問題を回避または制限するには、トップ(上層)デバイス層を525℃以下の低温で処理する必要があったが、今回の研究では、トップレイヤ上にジャンクションレストランジスタを形成することによって解決が図られ、かつ製造の複雑さも低減。十分なデバイスの信頼性を確保することができるようになったとする。

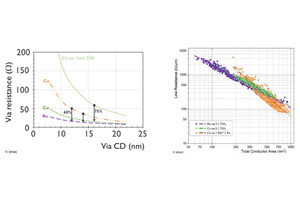

また、張り合わせの精度は、リソグラフィの性能にのみ依存し、ウェハアライメントの精度には依存しないため、チップ面積あたりのデバイス密度を向上させることが可能なほか、積層により、インタコネクトの長さ短縮ならびにRC遅延の低減も可能になるとしている。

なお、こうして525℃未満の温度で形成されたトップデバイス層は、VDD=1VでSS=72mV/dec、DIBL=80mV/V Ioff=1pA/μm、Ion=220μA/μmといったデバイス性能を実現したとするほか、ジャンクションレスのデバイスでは、さらにオン状態での酸化膜電界の低減により、信頼性向上のための高温アニールなしでも十分なNBTI/PBTI信頼性が確認されたとしている。