|

|

|

Xeon Scalable Processorを発表するIntelのAkhilesh Kumar氏 |

Hot Chips 29では、Intelは「Xeon Scalable Processor」と呼ぶ新プロセサを発表した。これは、これまで「Skylake-SP」と呼ばれていたプロセサである。Xeon Scalable Processorは、AMDのEPYCのような大変更はないが、バランスの取れた各種の改良が盛り込まれたデータセンター向けの新プロセサである。

従来、Intelのデータセンター向けCPUは「Xeon E5」とか「E7」とかいう名称であったが、今回の製品から、「Platinum」、「Gold」などという呼び方になった。

Xeon Scalable Processorは2016年Q2から出荷されているXeon E5、E7の後継となるサーバ用プロセサである。E5/E7が最大24コア、48スレッドであったのを最大28コア、56スレッドまで集積度を上げている。これまで複数のCPUチップの間を接続するバスは、QPIと呼ばれていたが、今回は、速度が9.6GT/sから10.4GT/sに向上し、UPI(Ultra Path Interconnect)と呼ばれることになった。Platinum、Goldと同様に、これらの名称変更はマーケティングであると思われる。

そして、PCI Expressのレーン数が40から48に引き上げられ、メモリチャネルは4チャネルから6チャネルに増強された。また、メモリバスの速度も2400MHzから2666MHzに引き上げられたので、両者の合計では、メモリバンド幅は67%向上することになり、これは大きな変更と言える。

ただし、消費電力は55W-145Wから70W-205Wと最大値で比較すると40%あまり増加しており、これも大きな変更である。

なお、LLCが60MBから38.5MBに減少しているのも大きな変更で、これは後述するように、2次キャッシュをメインとし、3次キャッシュ(LLC)を補完的な位置づけにするというアーキテクチャ的な考え方の変更の結果である。

次の図はSkylakeコアのマイクロアーキテクチャを示すものであるが、強化のポイントを以下に列挙する。

- 分岐予測器の改善、高スループットの命令デコーダ、大きな命令発行ウィンドウ

- 改善されたスケジューラと実行エンジン、除算とSQRTのスループットとレーテンシの改善

- ロードストアのバンド幅の増加、ロードストアのバッファの深さの増加、プリフェッチャの改善

- データセンター向けの改善であるAVX-512命令による2FMA演算/コア化、1MBのL2キャッシュ

となっている。また、実行資源の量が右上の表にまとめられている。これらの改良をみると、大部分が、これまであるものの改良や数量の増加であり、Skylakeコアで行われた改良は、現在のアーキテクチャの漸進的な改善であると言える。

ただし、データセンター向けの改善として挙げられているAVX-512のサポートとそれによる性能改善は、次の図に示すように、かなり改善効果が大きい。消費電力は、ほとんど変わっていないが、LINPACK性能は、AVX2では2034GFlopsであったのが、AVX-512で3259GFlopsまで1.6倍に伸びている。そして、GFlops/Wも2.92から4.38と1.5倍になっている。

アーキテクチャ的に大きく変わったのは、プロセサコアなどを接続するネットワークがリングバスから2次元メッシュになったことである。

次の左側の図に示すように、Xeon E7では、2つの2重リングのバスで24コアを接続していた。しかし、リングバスはコア数が多くなるとリングストップが多くなり、遅延が大きくなってしまうという問題がある。そこで、SkylakeではIntelもリングバスの使用を諦めて、2次元メッシュに切り替えた。

このスライドでは、メッシュにすることにより、バンド幅が向上し、レーテンシが減少したと書かれている。2次元メッシュはXeon Phi x200(Knights Landing)チップではすでに採用されているものであるので、切り替えには大きな問題はなかったと思われる。

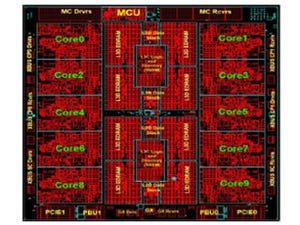

次の右側の図に示すように、2次元メッシュで6×6=36のタイルを接続しており、そのうちの28タイルがSkylakeコアで、2タイルが合計6チャネルのDDR4メモリコントローラ、2タイルがUPI、残り4タイルがPCIeとその他のI/Oに使用されている。

注目すべきは、Xeon Scalable ProcessorではL2キャッシュとL3キャッシュの位置づけを見直した点である。前世代のBroadwellでは、左の図のように、全コア共通のL3キャッシュはコア当たり2.5MBと大きく、L2キャッシュはコアあたり256KBとなっていた。この場合、L2とL3の比は10倍程度であり、伝統的な階層キャッシュの設計である。これに対して、SkylakeではL3キャッシュは1.375MB/コアに縮小し、その変わり、L2キャッシュをコアあたり1MBに大きくした。

伝統的な設計では、L3キャッシュがメインのキャッシュであり、L2キャッシュはその中の頻繁に使われる部分をキャッシュするという考え方である。これに対して、Skylakeでは、L2キャッシュがメインのキャッシュであり、L3キャッシュはL2キャッシュを溢れたものを格納するキャッシュと位置づけを変えた。そして、このスライドには、このキャッシュアーキテクチャはデータセンターの使用状況に合わせたものと書かれている。

もっともAMDのプロセサは、以前から、L2キャッシュがメインで、L3キャッシュはL2キャッシュを溢れたデータを格納するビクティムキャッシュであったので、やっと、IntelがAMDの方式の方がデータセンターに適していると気が付いたということかも知れない。

なお、この方式では、Broadwellのキャッシュのように、L2キャッシュにあるデータはすべてL3キャッシュにあるというインクルーシブな格納はできず、SkylakeのL3キャッシュはノンインクルーシブに変更されている。