(前編はコチラ)

NGVスパコンのアーキテクチャ

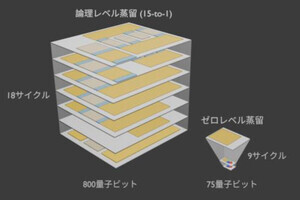

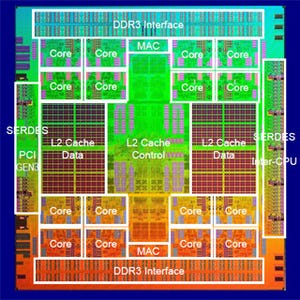

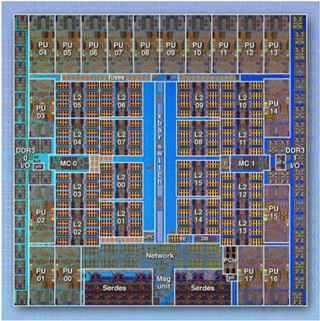

Cool Chips 16での百瀬氏の講演で初めて明らかにされたNGVスパコンのCPUの構成は次の図のようになっている。

CPUチップには4個のコアと16チャネルのDDR3メモリコントローラが搭載され、それらをクロスバで接続している。IntelのXeonでは上位のE7でもメモリコントローラは4チャネル、富士通のSPARC64 Xでも8チャネルであるのに対して、NGV CPUでは16チャネルという構成でメモリバンド幅を稼いでいる。また、SPARC64 XはDDR3-1600であるのに対して、NGV CPUではより高速のDDR3-2400あるいはDDR3-2666をサポートし、256GB/sというメモリバンド幅を持たせている。

|

|

次世代ベクトルスパコンのCPUチップは、4個のコアと16チャネルのDDR3メモリコントローラをクロスバで接続する。コアはスカラ処理を行うSPUとベクトル処理を行うVPU、そしてキャッシュ的な働きをするADBから構成されている。他の計算ノードは8GB/s×2のRCUを経由して接続される(出典:Cool Chips 16におけるNECの百瀬氏の発表スライド) |

各コアにはスカラ処理を行うSPU(Scalar Processing Unit)とベクトル処理を行うVPU(Vector Processing Unit)と1MBのAssignable Data Buffer(ADB)が含まれている。ADBは通常のCPUのキャッシュに相当するものであるが、CPUがアクセスするデータすべてを自動的にキャッシュするのではなく、再利用されるデータだけをユーザが指定して格納できるようになっており、容量が1MBと少ない割にはヒット率を高めるように工夫されている。

後で述べるようにVPUの倍精度浮動小数点演算性能は64GFlopsであり、これに対してADBのバンド幅は256GB/sであるので、VPUとADBの間では4Byte/Flopのメモリバンド幅を持っている。一方、ADBからクロスバへの接続バンド幅は64GB/sであり、通路が1/4に狭まっている。しかし、4コア合計では256GB/sであり、これはDDR3メモリへの256GB/sのバンド幅とマッチしている。

ということで、ADBからVPUにデータを供給し、VPUの演算結果をADBに書き戻すという演算では4Byte/Flopという伝統的なベクトルマシンのByte/Flop比を維持する設計となっている。そして、VPUとDDR3メモリの間でも1Byte/Flopであり、設計思想の所で述べた高メモリバンド幅を必要とするアプリケーションをカバーするという設計目標に見合った構成となっている。

CPUチップは28nmプロセスで作られ、23.05mm×24.75mmとかなり大きなチップである。消費電力は公表されなかったが、クロックは1GHzと低く、消費電力を抑えた設計になっていると考えられる。

この図に見られるように中心にクロスバとADBがあり、その上下に2個ずつコアが配置されている。そして、左右の辺に8チャネルずつのDDR3コントローラが載っている。そして、上の辺には2チャネルの×8 PCIeと12チャネルの10Gbit/sのシリアルポートが配置されている。

各コアに含まれるVPUのブロックダイヤは、次の図のようになっており、フロントエンドが命令を解釈し、16台のベクトルパイプラインに命令を発行する。

通常のプロセサの浮動小数点レジスタに相当するベクトルレジスタは64エントリで、各エントリは8Byte×256要素のベクトルを格納できる。ベクトル演算パイプラインは加算、乗算、ムーブとストアをそれぞれ2ユニット、割り算とSQRT、論理演算、マスクを各1ユニット持っており、最大256要素の長さのベクトルを1要素/サイクルで連続して処理することができる。

各ベクトルパイプラインは、1サイクルに2つの加算と2つの乗算を実行することができ、このベクトルユニットが16台あるので、VPU全体では1サイクルに64演算を実行できる。クロックは1GHzであるのでVPUあたりのピーク演算性能は64GFlopsとなり、CPUチップには4コアが搭載されているので、チップのピーク演算性能は256GFlopsとなる。

(後編に続く)