DPD形式とNUMBER形式の両方をサポートする唯一のプロセサSPARC64 X/X+

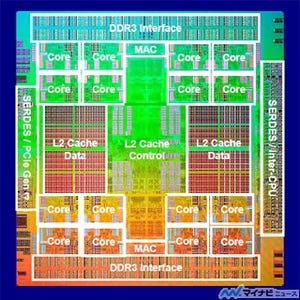

SPARC64 Xプロセサを使うマルチチップのシステムは、次の図に示すように4CPUのBB(Building Block)を基本とし、それをXBと呼ぶクロスバチップ群で接続するという構造になっている。

BBは4個のSPARC64 X/X+チップと2個のXBチップ、それに8チャネル分のメモリDIMMなどを含んでいる。下側左の図がBBの構成図で、4個のCPUが赤線のリンクで完全結合(どのチップ間にも直結のリンクがある構造)になっており、さらに、各CPUチップから2個のXBチップに白線のリンクで繋がっている。これらのリンクはSPARC64 Xでは、各方向、14/14.5Gbit/s×8bit幅のリンクであるが、SPARC64 X+では赤線のリンクのデータ伝送速度が25Gbit/sに高速化されている。

各BBの2個のXBチップからは各6本のリンクが出ており、これらのリンクは右側の図の中央に描かれたXBチップ群に繋がっている。2個のXBチップペアを3組含むXB-Boxが表側に2個、裏側に2個ある。

そして、BB#00~BB#03のグループは、一番上のXBペアを介してBB#04~BB#07のグループにつながり、2番目のXBペアを介してBB#08~BB#11につながり、XB-Box#2の一番上のペアを介してBB#12~BB#15と繋がるというように、どの4BBグループも他の4BBグループとXBチップ1個を経由(BB内のXBは数えない)して繋がると言う構造になっている。

結果として4個の4BBグループを相互接続することができ、最大64CPUチップ、1024コアのキャッシュコヒーレントな共通メモリのシステムを作ることができる。なお、キャッシュコヒーレンシの維持にはディレクトリベースのプロトコルが使われている。

次の図は、マルチチップの場合の性能向上を示すもので、一番上の線はJAVAの性能で、ほぼ理想的に64チップで64倍という性能になっている。また、その次のINTの場合も60倍強、FPとERPは50倍くらい、一番性能向上率の低いDWH(Data WareHouse)の場合でも47倍くらいの高いスケーラビリティーを示している。しかし、INTやFPがSPECint_rateやSPECfp_rateでの測定だとすると、同じプログラムを並列に流しているだけで殆どCPU間の通信がない。このような負荷だとすると、きれいにスケールするのは当たり前である。

そして、SPARC64 Xから、富士通はSWoC(SoftWare on Chip)と称して、暗号処理、十進数浮動小数点演算、データベース専用のソフトウェア機能をアクセラレートする命令を組み込み始めた。暗号処理用の専用ユニットや命令を持つプロセサは少なくないが、十進浮動小数点演算をサポートするプロセサは、他にはIBMのPOWERプロセサ程度で、珍しい。

通常のプロセサの浮動小数演算は2進数表現のデータを扱うが、ビジネス計算では十進数表現の浮動小数点計算が使われる。十進で0.1のようなありふれた数が、2進の場合、循環小数になってしまい、有限のビット数での表現では、わずかであるが誤差がでる。このため、利息が10%という計算が1円狂ってしまうということが起こり得る。また、事務計算は、科学技術計算に比べると計算量が少なく、入力時の十進→2進変換と、出力時の2進→十進変換のオーバヘッドが相対的に大きくなってしまうので、十進のままで計算するほうが効率が良い。

SPARC64 X/X+では、IEEE 754規格の固定長のDPD(Densely Packed Decimal)形式とOracleのデータベースで使われている可変長のNUMBER形式の両方をサポートしている。当然(?)IBMはOracle NUMBER形式はサポートしていないので、両方をサポートするプロセサはSPARC64 X/X+だけである。