スーパーコンピュータ「富岳」

富岳のCPUである「A64FX」はArm v8.2-Aにベクトル演算命令SVEを追加したアーキテクチャのプロセサである。ただし、アドレス空間が32bitの古い命令はサポートしていない。厳密にいえばこれはArmの仕様には合っていない。しかし、Armの32bit命令で作られたスパコン向けのプログラムがあるとは思われないので、実質上、互換性が問題になることは無いと思われる。

そして、浮動小数点数はFP64/FP32とAI計算用のFP16をサポートしている。ベクトル拡張のSVEでは512bitの幅広SIMD演算が実行できる。TSMCの7nm FinFETプロセスで作られ48の計算コアを集積し、これ以外に、OSなどを動かすアシスタントコアを2個、あるいは4個搭載している。

そして、アプリケーションチームから、高いメモリバンド幅が要求され、メモリチップを積み重ねるHBM2メモリを使う事にした。そのため、CPU1個当たりのメモリ容量は32GB固定となった。

CPUは7nm FinFETテクノロジを使い、dgemm実行時で15GFlop/W程度の高いエネルギー効率を実現する。クロック周波数はノーマル2.0GHz、ブースト2.2GHzである。

そして、CPUチップのピーク演算性能はノーマルモードでは3TFlopsで、dgemm実行時でもピークの90%以上の演算性能を出す。メモリバンド幅はピークでは1024GB/sで、stream性能はピークの80%以上となる。倍精度浮動小数点演算のメモリバンド幅と演算性能の比のByte/Flopsは0.33で、京コンピュータでの0.5よりは低下しているものの、0.1~0.2程度のスパコンが多い中、高メモリバンド幅のスパコンとなっている。

4個のCore-Memory-Groupはオンチップネットワーク(NOC)で接続されている。また、NOCはGMGとTofuインタフェースやPCIeコントローラを接続している。

なお、図25では異なるCMGのメモリは独立であるように描かれているが、実は4つのCMGのメモリは連続になっており、コヒーレンシも保たれている。もちろん、他のチップのCMGのメモリのアクセスは自分の属するCMGのメモリのアクセスより多少時間がかかるが、OpenMPを使う必要はない。ただし、一般的にはCMG内をOpenMP、 CMG(およびプロセッサ)間をMPIで行うか(この時はメモリアフィニティは気にしなくてよい)、プロセッサ内をOpenMP、プロセッサ間をMPIで行うか(プロセッサ内のメモリアフィニティに注意が必要)というモデルが使われるとのことである。

2021年6月15日追記:2021年5月27日に、「もちろん、他のチップのCMGのメモリのアクセスは自分の属するCMGのメモリのアクセスより多少時間がかかるが、OpenMPを使う必要はない。したがって、富岳のプログラム複数CPUチップの間の処理分散はOpenMP、あるいはMPIで処理分散というモデルとなる。」と記事を修正させていただいておりましたが、OpenMPを使用する場合もあるため、当該箇所を改めて適した形に修正させていただきました

図26は、左はCPUチップと4個のHBM2メモリを搭載したパッケージの写真で、少し上下がへこんでいる部分がCPUチップである。そして、よく見ると、左右の少し長い辺のところは中央に横線が見える。これが4個のHBM2メモリの切れ目である。これらのチップの下にはインタポーザと呼ぶシリコンの配線基板があり、その基板にCPUとHBM2チップを接続する配線が作られている。

図26の右側はCPUチップのダイ写真である。上下と左右に2分したものの1つがCMGで、Coreと書かれた領域が13個見られる。これが4組あり、チップ上には52コアが作られていることが分かる。そして、左右の辺の上下にHBM2のインタフェースが作られ、上の辺にTofuインタフェースとPCIeインタフェースが置かれている。

次の図27はA64FXを左に置き、右側にIntelのSkylake CPUを右側に並べた図である。両者の縮尺が一致するようにスケールされており、実物のチップを並べた場合と同様に見える。Skylakeの方が若干大きなチップであるが、集積するコア数は18である。一方、A64FXは48コアと約2.7倍のコアを集積している。そして、Skylakeはチップサイズも20%程度大きいので、コア密度では3倍程度の違いがある。

ただし、A64FXは7nmプロセスであるが、Skylakeは14nmプロセスであるので、この程度のチップ面積の違いは使ったプロセスの差であるともいえる。

Tofu Dは6次元のメッシュ/トーラスネットワークを構成し、6台のRemote DMAエンジンを持ち、6.8GB/s×6=40.8GB/sの転送バンド幅を持つ。そして、バリア機能をサポートするハードウェアを持っており、Allreduceなどを高速化している。

8BのパケットのPutのレーテンシは0.49-0.54μsで1MBのデータをPutする場合のバンド幅は6.35GB/sである。

図29のピンポン転送(受け取ったメッセージを時間を置かず直ちに打ち返す転送)のレーテンシをみると、京コンピュータの場合はメッセージサイズが100バイトを超えるあたりからレーテンシが長くなっていたが、富岳では数千バイトまで比較的短いレーテンシとなっている。また、1MBの転送の場合のスループットは、京コンピュータでは4.5GB/s程度であったが、富岳では6GB/s程度に向上している。

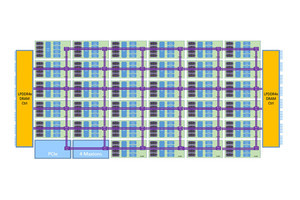

富岳は図30のような構成になっており、全体では158,976ノードと言うシステムである。ノードにはComputeノードとCompute & I/Oノードがある。

富岳のストレージは3階層になっており、第1層は16 Computeノードの中の1つのノードに接続された1.6TBのSSDへの記憶で、このストレージはファイルシステム全体のキャッシュとなっている。また、このストレージはComputeノードのローカルファイルシステムなどの一時的なファイルの格納にも使われる。第1層のストレージのスループットはWriteでは125MB/s/node、Readでは293MB/s/nodeとなっている。

第2層のストレージは約150PBの容量を持つ富士通のFEFSストレージである。第2層のストレージのスループットはWriteでは220GB/s/volume、Readでは211GB/s/volumeとなっている。

そして第3層のストレージはクラウドのストレージサービスを利用する。

(次回に続く)