京都大学(京大)は10月21日、SiCの欠陥(不完全性)を独自手法で低減することで、実用的なトレンチ構造のSiCトランジスタの性能を従来比で6倍以上向上させることに成功したと発表した。

同成果は、同大大学院工学研究科の木本恒暢 教授、立木馨大 博士後期課程学生らの研究グループによるもの。詳細は、2021年10月26日にSiC半導体に関する「ヨーロッパ会議(ECSCRM)」にて発表された。

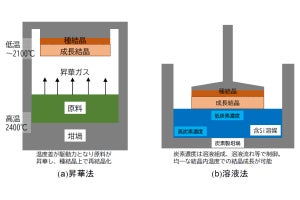

次世代パワー半導体材料として期待されるSiC。長年、酸化膜とSiCの境界部分(界面)に多くの欠陥が存在することが、特性や信頼性を制限することとなり、材料本来が持つ性能までデバイス性能を引き出すことが難しいとされてきた。近年になって、さまざまな界面欠陥の低減手法が考案されるようになってきており、研究グループでも2020年に、SiCを酸化せずに良質の酸化膜を形成することを可能とする堆積法を用いた独自手法を活用することで、SiCトランジスタ性能を従来比で2倍以上に高めることができることを報告していた。

今回の成果は、この研究を発展させたもの。具体的には、理想的な構造であるトレンチ型SiC MOSFETの垂直面(A面ならびにM面)の基板に堆積法を用いて酸化膜(SiO2)膜を形成することで、表面平坦性が従来法に比べて向上すること、ならびに界面欠陥密度(総量)がSi面(従来法)で5.1×1010cm-2であったのが、2020年の発表のSi面(独自手法)で2.2×1010cm-2、今回のA面では1.2×1010cm-2、同M面では0.8×1010cm-2と、低減することに成功したとする。

また、トランジスタの耐電圧の増大や信頼性向上に必要な高濃度不純物(Al)をドープしたp型SiCにおけるチャネル移動度は、ドーピング密度を実用レベル(1017~1018cm-3)を超す5×1018cm-3まで高くした場合、独自手法のM面で従来手法比で80倍(80cm2/Vs)に高まること、1017程度であっても独自手法のA面で従来手法比で6倍(131cm2/Vs)ほどに高まることを確認したという。

この性能向上が実現できた理由について木本教授は、酸化膜とSiC界面の平坦性が優れており、電子の散乱が減少したためであると考えられると説明しているが、理論上では200cm2/Vs~250cm2/Vsほどまで高められると考えられているため、欠陥や界面の不完全性を徹底的に減らすことで、さらなる性能向上を図っていきたいとしている。

また、今回考案された技術は既存のトレンチMOSFETの製造プロセスに数プロセスを追加するだけでできると考えられるとしており、コスト的な問題も発生しないと考えられるとしている。ただし、プロセス的には問題ないとしても、あくまで大学の実験室で製造できる小片SiCで評価した結果であり、実際の量産で用いられるサイズの6インチなどの大きな口径のウェハ面上の均一性がどの程度になるのか、といった点については、別途評価する必要があるともしている。

もし、今回の技術が実際のSiCパワーデバイスとして適用できれば、仮にチャネル移動度が従来比で6倍に向上した場合であっても、オン抵抗を約50%低減できるため、同じ定格電流を半分のチップサイズで実現できるようになり、ウェハ品質の向上による歩留まり向上もあいまりコストを約6割低減することができるようになるとするほか、ゲート酸化膜厚を2倍にしても十分低いオン抵抗を達成できるため、信頼性の向上を図ることも可能になると研究チームでは説明している。