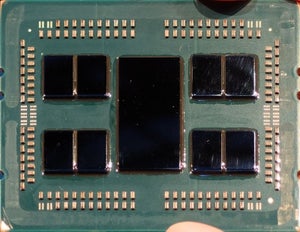

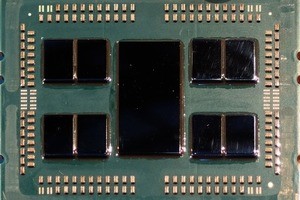

とりあえず会場から速報ニュースだけお送りしたAMDの第2世代EPYCであるが、実際はDeep Diveに加えて色々な性能評価結果なども示された。本稿ではこのあたりをまとめて、第2世代EPYCレポートのDeep Dive編としてご紹介したいと思う(Photo01)。

-

Photo01: 第2世代EPYCを紹介するLisa Su CEO。第3世代Ryzen/Radeon RX 5700の時は皮ジャンだったのが、EPYCではスーツというあたりはやはりビジネス向けを意識しているということか?

◆内部構造

第2世代EPYCも、初代EPYC同様CPUダイはRyzenと共通である。なので、こちらの記事で紹介したZen2コアの特徴はそのまま引き継いでいる。異なるのはそのCPUダイをどう繋ぐか、という事である。Photo02は従来(=IntelのXeon系列や、過去のOpteron系)の接続方式から初代EPYC、そして第2世代EPYCの結合方式をまとめたものである。結果としてI/O Chipletは巨大になったが、全体としては効率的な構成になったと言える。

-

Photo02: すくなくとも第2世代ではRoutingの手間が簡単になった(以前は各々のCPUダイが3本のInfinity Fabricのどのレーンを使うか、を各ダイが判断する必要があった)のは間違いない。

加えて、Infinity Fabricそのものも高速化された(Photo03)。元々、こちらの分析のグラフ35とかグラフ36でも示している様に、Zen2ではInfinity FabricのLatecnyが大幅に短縮されており、あるCCXから同一または別のダイへのCCXへの通信は70~90ns程度のLatencyになっている。Zen+コアの場合、同一ダイ上の2つのCCXの通信のLatencyが120ns程度だったから、ほぼLatencyが2/3になった計算である。勿論第3世代Ryzenと第2世代EPYCが同じLatencyという保証はない(大規模になっている分、若干Latencyは増えている可能性はある)が、少なくとも初代EPYCに比べればずっと高速と考えられる(初代EPYCのLatencyは、概ねRYZEN Threadripper 2950Xとか2990WXに近いと考えられる。こちらは以前のThreadripper 2のレビューでご紹介した通り、異なるダイ間の通信のLatencyが250ns程度となっている)。

さらに加えて、Photo03にあるように

CPU Chiplet⇔I/O Chiplet:48Bytes/cycle

I/O Chiplet⇔I/O Chiplet:18GT×2×4

となっている。まずCPU ChipletとI/O Chipletは第3世代Ryzenと同じく、32Bytes/cycleのRead(I/O Chiplet→CPU Chiplet)+16Bytes/cycleのWrite(CPU Chiplet→I/O Chiplet)という構成である。このCycleはFCLKに同期する、というのも第3世代Ryzenの構成と同じで、仮にDDR4-3200を利用時なら合計で38.4GB/secに達する計算である。初代EPYCだとこれは25.6GB/secでしかなかった。

また2 Socket構成の場合、従来はPCI Expressレーンを利用して10.7GT/secで相互接続していた(レーン数は合計64)が、第2世代EPYCでは相互接続専用PHYが別に用意されており、こちらは18GT/secまでスピードが引き上げられている。勿論従来のNaplesプラットフォーム上で第2世代EPYCを使う場合、互換モードで動作するのでPCI Expressレーンを利用して10.7GT/secでの接続となるが、今回第2世代EPYCにあわせて発表されたRomeプラットフォームだと、より高速に接続が可能となる。Latencyが下がり、帯域が上がれば当然性能の向上に繋がる訳で、ここは大きなポイントである

なおLatencyについては、NUMAモードにおけるLatencyが示されている(Photo04)が、初代EPYCの場合はそれぞれのCPUダイごとに1つのNUMAノードを構成する形になっており、同一ダイ上のCCX間は90ns、同一パッケージ上の異なるダイ間は141ns、異なるパッケージ間は234nsなのに対し、第2世代EPYCでは同一パッケージ上が104ns、異なるパッケージ間も201nsに短縮されているとする。

-

Photo04: ただNUMAを細かく分割したい、という場合には第2世代EPYCはちょっと不利になる形である。1つのパッケージ上で複数のNUMAノードを構成するようにパーティショニングできるかどうか、は現状不明である。

ちなみにこの18GT/secのPHYはSATAポートなどの接続にも流用可能になっており、なのでレーン数は「最大4対」という表現になっているほか、速度も色々変更可能となっている(Photo05)。最大の18GT/secの場合、理論転送帯域は18GT/s×16bit×8=288GB/secとなる計算で、実効でも202GB/secに達するとする。初代EPYCだと理論転送帯域ですら10.7GT/s×16bit×4=85.6GB/secでしかないから、3倍以上高速化された形だ。

その一方でメモリは引き続き8chに据え置きになった(Photo06)。これはちょっと解せなかったので、講演の後で「なぜ16chにしなかったのか」と質問したところ「8chのままでもL3キャッシュの大容量化とDDR4-3200のサポートで、性能は十分スケールする(から16chは不要だった)」という返事が返ってきた。端的に言えば、一つのSocketから16ch分のDDR4を引っ張り出すことは無理ではないにせよ、配線的にかなり厳しいのは間違いない。

策が無いかといえばそうでもなく、例えばOpenCAPI向けのMemory Interfaceとして新たに提唱されているOMI(Open Memory Interface)向けにMicrochipから先日発表されたSMC1000 8x25Gという一種のBridge Chipを利用すると、Registered DDR4-3200の72bit分の信号線を8bitの信号に変換してホストに接続するといった技はあるのだが、Bridgeを挟む分Latencyは増えるし、BOMコストも上がる。おまけにCPUとこのBridgeの間は25GT/secの信号が通るので、配線が厳しい事にはあまり変わりが無かったりする。この辺りを勘案して、メモリを8chに据え置きにしつつ、ただしコアの数が倍増するのにあわせてL3キャッシュを2倍に増加させたことで、バランスを取ったというのが正確なところだろう。実際AMDの説明によれば、コアの数と性能がスケールする(メモリ帯域が倍にならなくても、性能がほぼ倍になる)としており(Photo07)、実質的には支障ないという返事であった。

-

Photo07: 左はおそらくSPEC CPUの、右はSPECjEnterpriseあたりの結果ではないかと思うが、詳細は不明。32c64t→64c128tがメモリ帯域の影響を受けそうなところだが、ほぼCore/Thread数にScaleして性能が伸びているとしている。

メモリ搭載量そのものは、今回4TB/Socketとされている。初代EPYCは2TB/Socketという話であったが、確認したところ「初代EPYCの時は8GbitチップがDRAMの最大容量だったが、今は16Gbitチップが入手可能であり、このためDIMM容量を2倍にすることが出来た」のが最大の違いだそうである。この16Gbitチップを搭載したDIMMを使えば、初代EPYCでも理論上は4TB/Socketのメモリ容量を実現可能だが、それにはマザーボードメーカーのBIOS Updateが必須という話であった。

ところでPCI Expressであるが、1 Socketあたり128Lane(8×16)というのは以前と変わらない。ただ、16Laneあたり8台までDeviceを接続できるようになったので、例えば間にPCI Express Switchを挟むと従来のGen3×4 NVMeSSDを8枚ぶら下げる(SwitchでGen3×4をGen4×2に変換する)なんて事も可能になった。またPCI Express P2P(PCI Expressデバイス同士での直接の通信:例えばアクセラレータ同士がCPUを介さずに通信する)も可能になっている。

面白いのは2 Socketの構成である。初代EPYCの場合、各々のSocketから128LaneのPCI Expressが出たが、うち半分の64LaneはInfinity Fabricを利用してのSocket間通信に転用されたので、I/O向けにはそれぞれのSocketから64Laneづつ、合計で128Laneという構成だった。これに対し、第2世代EPYCではSocket間に専用Linkが使えるため、PCI ExpressはSocketあたり81Lane、2 Socket合計で162Laneが利用可能となっている。もっとも先のSATA転用の話などを勘案すると、相互接続用のうち32Lane分(Photo03の右側で、"SATA compatible on lower 8 lanes"とある破線のもの)はPCI Expressとピンが共用になっているのかもしれない。とはいえ、2 Socket Serverで10枚のPCI Expressアクセラレータを搭載し、更に管理用あるいは通信用などにPCI Express 2x1が利用できる形なので、普通に考えればこれで十分であろう(アクセラレータが8枚+InfiniBand HDR or 200G Ethernetカード×2、というあたりがあり得る構成だろうか)。

-

Photo08: 当然ながらPCI Express Gen4として動作するのはRome Platformのみで、Naples Platformを利用する場合にはPCI Express Gen3相当となる。この場合は2 Socketでも合計64 Laneのみが利用可能となる。

話は変わるが、初代EPYCとかRyzen Proでは、Ryzenでは無効にされていたセキュリティ機能が有効化されている。これは第2世代EPYCでも同じで、従来同様Cortex-A5をSecurity Processorとして搭載する(Photo09)他、SME(Secure Memory Encryption)/SEV(Secure Encrypted Virtualization)も引き続き利用できる(Photo10)。

-

Photo09: これはMerlin Falconかなにかのダイ写真と思われる。ちなみにこのSecurity Processorが物理的にどこにあるのかは明らかにされていない。なんとなくこれはI/O Chipletの側に搭載されている様に思うのだが、確証はない。

-

Photo10: 509という数字も不思議だが、実際にはキーは512種類あり、うち3つはInternal Useに確保されているというあたりだろうか?

大きな違いは、このMemory Encryptionで、暗号化方式は従来同様AES-128であるが、初代EPYC(というか初代Zen)が15種類の暗号化キーを利用可能だったのに対し、第2世代EPYCではこれが509種類に拡充されている。例えばHypervisor上で複数のVMを動かす、なんてケースでVM毎に異なるキーを利用することで、あるVMが他のVMのメモリの内容を参照できない様に防御したい、というのは普通の要求だと思うが、初代だと15種類しかキーが無いから、どうしても使いまわしは避けられなかった。

ところが今回509ものキーを利用可能になったので、それこそ500以上のVMを同時に動かすといったケースでない限りほぼ問題なくVM毎にキーを分けられるようになった。またこれを利用する場合、VM内で明示的に暗号化キーを利用する必要があるが、今回Virtual-transparent-encryptionの機能が追加され、VM側が未指定でも暗号化を利用できるようになった(Photo11)。このSEVであるが、既に初代EPYCでほぼ最新のOSの対応は終わっており、第2世代EPYCでもそのまま利用可能となっている(Photo12)。

-

Photo11: Hypervisor側で透過的なメモリ暗号化処理の設定を行うことで、Guest VMは意識せずにメモリ暗号化の恩恵を受けられるようになった。

-

Photo12: 会場ではVMwareが動作デモを行っており、製品出荷は"Coming soon"としていた。

最後にパフォーマンスの話を。ラインナップは後述するが、今回TDPは最大240Wになっており、ほぼ180W(EPYC 7371のみ例外的に200W)だった初代EPYCに比べるとややTDPは大きくなっている。ただしConfigurable TDPをサポートしており、初代EPYCと同じTDP枠にすることでそのままアップグレードも可能な形に配慮している。

それはともかくとして、やはり動作周波数は動的に変化するのだが、最大動作周波数を見ると8コアで3.4GHzなのが64コアで3.2GHz、とコア数の変化の割に最大動作周波数に差が無い(Photo13)。コンシューマ向けの第3世代Ryzenでは4GHz超えであるが、サーバー向けでは最大動作周波数はかなり低めに抑えており、ワークロードの変化に応じて性能がコア数にScaleするような電力管理が行われている事が明らかにされている。

-

Photo13: コアの単位が8、ということでこれはダイ単位での制御になるが、ただし実際にはダイの中でも更にコア単位での動作周波数制御が行われている模様だ。なおこれも余談になるが、やはりI/O Chipletの側にOn-die RAMの形でDirectoryを持っており、これでCoherent制御を行っているものと思われる。まぁこれは妥当な実装だろう。

もともと初代のEPYCとRyzen、Ryzen Threadripperでは

Ryzen Threadripper:高動作周波数のコアを選別

EPYC:安定性の高いコアを選別

Ryzen:普通のコアを利用

といった形で作りわけがされており、これは第2世代EPYCでも恐らく同じ様になされているものと思われる。恐らくはこの第2世代EPYCでは、Ryzen 7/9向け程には高速動作はしないが、その代わりに動作周波数が上がっても消費電力の上がりにくい、安定したコアを選別して利用していると思われ、そうした事もこのグラフの特性の獲得に貢献しているのだろう。

ところでこのPhoto13、何気に"No turbo limitations based on instruction mix"とあるのは、IntelのAVX2/AVX512 Offsetへの当てこすり、と考えて良いだろう。要するにAVX2あるいはAVX512をフルに動かすとThermal/Power Limitを簡単に超えてしまうので、AVX2/AVX512をある程度連続して稼働させるときには自動的に動作周波数を落とす仕組みが用意されている。こうした配慮は第2世代EPYCには不要、というメッセージである。