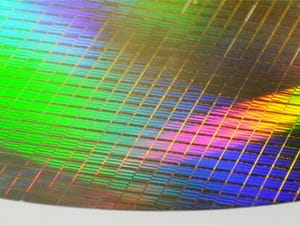

東芝メモリは、TSV技術を用いた3ビット/セル(TLC)の3次元NAND型フラッシュメモリ(3D NAND)「BiCS FLASH」を開発、試作品の提供を開始したことを発表した。

今回、同社は48層積層プロセスを用いた3D NANDにTSVを適用することで、書き込みバンド幅と低消費電力性能の向上に成功。電力効率がワイヤボンディングを用いた製品比で約2倍に向上した。また、512Gビットのチップを1つのパッケージ内に16段積層することにより、1パッケージで1TBを実現した。

試作品の主な仕様は、以下の通り。

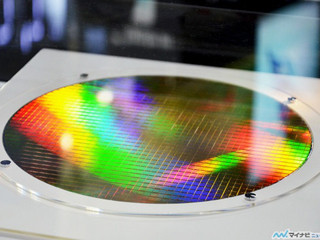

なお同社では、2017年中に製品のサンプルを出荷する方向で予定している。また、試作品については8月7日~10日まで米国にて開催されるフラッシュメモリの国際会議「Flash Memory Summit 2017」で参考展示される予定だという。