独立系半導体ナノテクノロジー研究機関であるベルギーimecは、米国サンフランシスコで7月11~13日に開催された半導体製造装置の展示会「Semicon West 2017」に併催される形で開催された「imec Technology Forum 2017 USA」において、imecの設立母体であるベルギーKULeuven(ルーベン・カトリック大学)および伊Pisa大学と共同で、10nm未満の高性能ロジック用途に向けて、2次元材料を用いたFETの材料・デバイス・回路の3要素同時最適化に成功したことを明らかにした。また、単層2次元材料を使って、ムーアの法則を5nmゲート長未満にまで延命することのできる新規設計手法も公開した。

2次元材料は、2次元の結晶を形成する材料の総称であるが、これを用いると、単原子層の薄さのチャンネルと数nmの短さのゲート長をもった究極のトランジスタを形成できる。

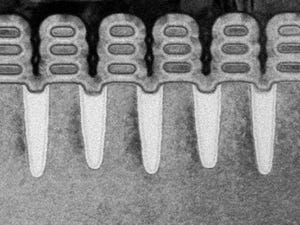

半導体業界がムーアの法則にしたがって成長を続けてきた背景には、プロセスの微細化によってゲート長のスケーリングが為されてきたためだ。しかし、微細化が進んだことにより、逆にトランジスタに悪影響を与える短チャネル効果が発生するようになり、先端プロセスを活用したい半導体メーカーは、従来の平面型のトランジスタから3次元化したFinFET(3次元トランジスタ)に移行することで、この問題を避けることに成功した。これから先の微細化については、ナノワイヤFETのような新たなトランジスタアーキテクチャも開発されているが、今回のimecらの研究報告は、トランジスタのチャネル材料を2次元材料で置き換えることで、その先に進もう、というものとなっている。

2次元材料をチャネルに用いたFETをスケーリングのロードマップに適合させるには、その特性がデジタル回路の挙動にどのように関連しているかを理解することが不可欠である。 Natureが発行する「Scientific Reports」に掲載された今回の研究に関する論文によると、、10nm未満の高性能ロジックチップの要件を満たす回路を実現するために、研究グループは最初に材料の選択を行った後、デバイスの設計、そしてシステム性能を最適化する方法に関するガイドラインを提示。そして異方性があり、搬送方向の有効質量が小さい2次元材料を使用する必要性を示し、そのような2次元材料である単原子層の黒リン(Monolayer BP:MLBP)を用いて、ムーアの法則を5nm以下のゲート長にまで延命できる新たなデバイス設計手法を公開した。

これらの設計手法によって、5nm未満のゲート長では、ゲートスタック構造から生じる2次元静電容量が、直接的なソース-ドレイン間トンネリングよりも困難になることも明らかにしており、これらの結果は2次元材料を用いたFETが将来的に有望であることを示すものとなる。Siなどの3次元半導体材料の場合、ゲート長を今以上に積極的に縮小することは事実上不可能であるからである。

なお、imecの技術スタッフであるIuliana Radu氏は、今回の研究について、「2次元材料は、原子レベルで正確な寸法制御が可能で、将来のトランジスタ技術に革新を起こす重要な材料となることが見込まれている。研究が進展するにつれて、フォトニクス、オプトエレクトロニクス、バイオセンシング、エネルギー貯蔵、太陽光発電、トランジスタスケーリングなどの分野で新たな機会が生まれて来るだろう。実際、これらのコンセプトの多くは、すでに研究室レベルでは実現可能性が見出されている」と述べており、今後のエレクトロニクスの進化の鍵を握る可能性があるとしている。