ベルギーimecは、去る6月5~8日に京都で開催された「2017 Symposia on VLSI Technology and Circuits(「VLSIシンポジウム国際会議)」において、世界初の成果を含めた次世代半導体プロセス・デバイス技術について4件の発表をおこなった。

これらの研究は、すべてimecの半導体技術およびシステム研究開発担当エグゼクティブバイスプレジデント(EVP)を務めるAnn Steegen氏の陣頭指揮の下でベルギー・ルーベン郊外に設置されているimecのクリーンルームにて研究パートナーたちとの協業により進められてきたものだ。

5月16-17日にかけてベルギーで開催された「imec technology Forum」における同氏の次世代半導体プロセス・デバイス技術に関する講演では、学会発表前の規制のために研究内容の詳細は紹介することはできなかったため、詳細が明らかにされたのはVLSIシンポジウムが初めてということとなる。

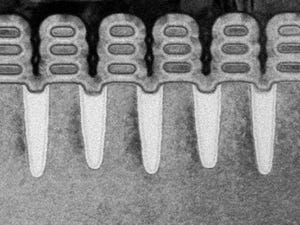

世界で初めて10nm未満プロセスで歪みGe GAAデバイスを試作

1つ目の成果は世界で初めて、歪みゲルマニウム(Ge) pチャンネル ゲートオールアラウンド(GAA) FETを10nm未満のプロセスで300mmシリコン基板上に形成することに成功したというもの。高圧アニール(HPA:high pressure anneal)を採用することにより、歪みGe pチャネルFinFETおよびGAAデバイスの両方ともに、デバイス特性と電界制御を改善することで実現したという。

GeやIII-V属化合物のような半導体材料は、材料本来の性質としてキャリア移動度が高いため、10nm未満の超微細デバイスの潜在的な解決策と考えられてきた。しかし、これらの材料は、シリコンよりも誘電率が大きくバンドギャップが小さいため、微細化でゲート長が短くなるにつれて、電界制御がますます困難になる。この問題を解決するには、電界制御しやすい新しいデバイス構造が必要になっていた。

imecでこの技術開発を担当した研究スタッフであるNadine Collaert氏は、「以前、公開した14/16nm技術ノードの歪みGe p-FinFETのプロセスフローを見直し、短いゲート長での歪みGe GAA p-FETの利点を研究し、最短ゲート長(LG=40nm)と、これまでに報告されたものの中で最小のナノワイヤ直径(d=9nm)によるGAA p-FETの試作に成功した」とし、これらの短ゲート長でも優れた電界制御が可能になった。ドレイン誘導障壁低下は30nm/v、サブスレッショルドスロープは79mV/dec.と測定された。

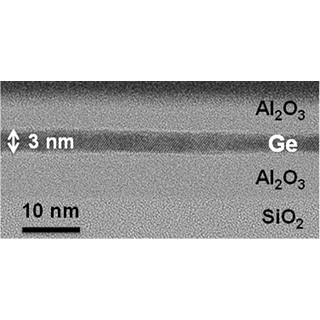

高圧アニールの活用により特性を改善

2つ目の成果は、Ge FinFETとGAAデバイスの双方に適用可能な新たな性能向上手法としての高圧アニール(HPA)技術。450℃でHPAを行った結果、良好な界面特性とホールの移動度の向上(~600cm2/Vs)が実現できたという。GAAデバイスの電界効果やデバイス性能も格段に改善したという。具体的には、ゲート長60nmの場合、SSLINは65mV/dec、IOFFは3×10-9A/μmと低く、Qファクタは15であったという。

MOSトランジスタ向け低ソース/ドレイン・コンタクト抵抗技術を開発

3つ目の成果としては、P型MOSトランジスタのソース/ドレイン・コンタクト抵抗として10-9Ωcm2未満という低い値を達成した点。このような低い値は、p型SiGe(p-SiGe)ソース/ドレイン・コンタクト上にガリウム(Ga)を浅く注入し、その後にナノ秒レーザーアニールを行って得られたという。

次世代の7~5nm技術ノードでは、トランジスタのソース/ドレインへのコンタクト部分の面積が非常に小さくなり、結果としてコンタクト抵抗が大きくなり、最適なトランジスタ性能が得られないという問題がある。このため、世界中の研究者たちは、高ドープn-Siおよびp-SiGeソース/ドレインコンタクト部の接触抵抗を低減する技術の研究を進めており、ターゲット値として10-9Ω・cm2未満の値を目指している。

imecのエンジニアたちも、ベルギーのルーベン・カトリック大学(KULeuven)、中国上海の復旦大学、米国カリフォルニア州サニーベールのApplied Materialsなどと協力して、p-SiGeコンタクトに対する高濃度のGa(ガリウム)およびB(ホウ素)のイオン注入の比較検討を実施したほか、さまざまなアニール条件に変更して実験を進めたという。また、それぞれの条件下で得たウェハ上にマルチリング円形伝送線モデル構造を形成し、コンタクト抵抗の測定を実施して、比較を行った。ちなみに、同構造を選んだのは、コンタクト抵抗にきわめて敏感だからであるという。

比較検討の結果、Gaをイオン注入した後、Applied Materialsのナノ秒レーザーアニール装置でアニールした場合で一番低いコンタクト抵抗値が得られることが判明した。具体的には、このプロセスにより、Ge/Gaの特異な表面偏析が生じ、10-9Ω・cm2未満のコンタクト抵抗が得られることが分かったとする。

この成果について、imecの日本人技術スタッフである堀口直人氏は、「7~5nmの技術ノードに向けた今回の研究成果は、現行の7~5nm技術ノード向けソース/ドレイン構造を使用しつつ、さらなる性能向上に向けた道を切り開いた」と説明している。

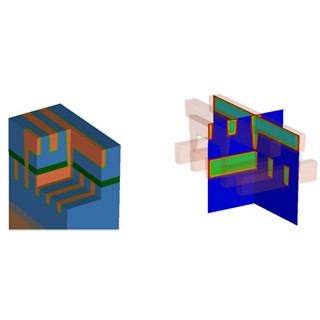

世界初となるCMOSコンパチブルHfO2強誘電体メモリ

4つ目となる成果は、世界初となるNAND型強誘電体AlドープHfO2デバイスのデモの実施である。実際に動作を見せることで、imecは、新材料と新アーキテクチャによる、消費電力、スイッチング速度、スケーラビリティ、および記憶保持といった性能面で魅力的な特性を備えた新たな不揮発性メモリの概念を樹立できたことをアピールしたこととなる。また、この成果は、強誘電体メモリが記憶階層のさまざまな点で有望な技術であり、いわゆるストレージクラスメモリのための新しい技術であることを明示するものであり、imecによると、世界をリードする半導体メモリメーカーと協力してこのコンセプトをさらに発展させる計画としている。

50年以上前に発見された強誘電体メモリは、消費電力が非常に少なく、不揮発性であり、スイッチング速度が速いため、常に理想的な不揮発性メモリあると考えられてきた。しかし、複雑な材料構成、界面層のブレークダウン、および保持特性の悪さの問題があり、実用化の妨げになってきた。しかし近年、MOSデバイスのHigh-kゲート絶縁膜材料としてよく知られた、複雑ではない材料であるHfO2が強誘電特性を備えていることが発見されたため、強誘電体を利用した記憶概念に対する新たな関心が引き起こされることとなった。

「HfO2を用いることで、CMOS互換の強誘電体メモリを作製することができるようになった。これにより、私たちは平面型と垂直型の両方で強誘電体FET(FeFET)を製造することができるようになった」と、imecのメモリ技術担当チーフ・サイエンティストであるJan Van Houdt氏は述べている。

また、「FeFETは、フラッシュメモリと非常によく似たメモリを構築する技術として使用できるが、微小化が可能、製造プロセスが簡単、消費電力が少ないといったメリットもある」としたほか、「我々は、強誘電相を安定化させるために、記憶保持、正確なAlドーピング技術および界面特性などの残りの問題のいくつかを克服するよう努めており、すでにFeFETのコンセプトが不揮発性メモリに必要とするすべての必要な特性を持っていると確信している」と説明しており、不揮発性DRAMからフラッシュのようなメモリまで、メモリ階層内のさまざまなポイントでスタンドアロンメモリと組み込みメモリの両方に適しているとする。この特性により、高速プロセッサと、より低速の大容量メモリの間の速度の違いによって引き起こされる現在のボトルネックを克服するのに役立つだけではなく、将来のストレージクラスメモリにとって特に興味深いものとなるだろう。すでにimecは、世界中の大手メモリメーカーを含む、すべてのメモリパートナーへのプログラムとして、垂直FeFETの実用化情報を提供しているという。

なお、これらimecが明らかにした次世代デバイス・プロセスに関する研究成果は、GLOBALFOUNDRIES、Intel、Micron Technology、Qualcomm、Samsung Electronics、SK Hynix、ソニーセミコンダクタソリューションズ、東芝、SanDisk、TSMCなどの主要研究パートナーとの協業によってもたらされたものである。