1:世界初、8nm Siナノワイヤを積層した横型GAA FETを発表

「2016 Symposia on VLSI Technology and Circuits(VLSIシンポジウム 2016)」が、「スマート社会への変革の予兆」をメインテーマに、2016年6月13~17日に米国ハワイ州ホノルルで開催された。その中で半導体プロセス・デバイス技術を主に扱うこの国際会議で、ベルギーの独立系半導体研究機関imecが、直径8nm Siナノワイヤを基板に水平な状態で縦方向に2段積層したゲート・オール・アラウンド(GAA) n型およびp型MOSFETを発表した(図1)。imecによれば、このような構造を10nm未満のプロセスで実現したのは、世界初ということで、シンポジウム主催者も、事前に最も注目される発表の1つに選んでいた。

水平なナノワイヤを垂直積層しゲートで取り囲む

このデバイスは、以下に述べる3種類の特徴的な構造を組み合わせることにより、はじめて10nmを切るナノワイヤ積層GAA FETを実現した。

- チャネル領域を四方から包み込むGAA構造:能力を最大化し、待機時のリーク電流を最小化する観点から、究極のMOSデバイス構造として注目されている

- 横型ナノワイヤ構造:ナノワイヤを垂直方向に形成するには、新規なプロセスを採用しなければならないのに対して、基板に水平なナノワイヤは、一般的なRMG(Replacement Metal Gate;置換メタルゲート) FinFETの延長として比較的簡単に形成できる。RMGは、日本ではゲートラストと呼ばれる場合が多い、確立したプロセスである

- ナノワイヤを垂直方向に積層する構造:駆動電流を増やすとともに、短チャネル効果を抑えられる

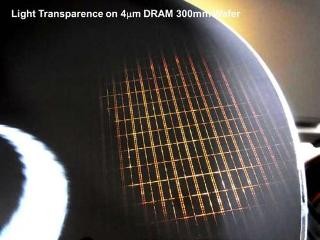

なお、今回試作したGAA FETのナノワイヤの直径は8nm、Finの水平ピッチは45nm、縦方向の素子分離距離は20nmである(図1)。

|

|

|

図1 ゲート・オール・アラウンド横型Siナノワイヤ FETアレイ断面の透過型電子顕微鏡写真と2つのシリコンナノワイヤを積層したFET部分の拡大写真 (出所:2016 VLSI Symposium広報資料) |

基板へのドーピングで寄生チャネルを抑止

従来のバルクFinFETの製作フローに比べて 今回のデバイス製作フローは2つの点で大きく異なるとimecはいう。(1)シャロー・トレンチ・アイソレーション(STI: 極薄素子分離)構造緻密化を750℃で行うことにより, SiGe/Si界面をシャープに保てた。これは、ナノワイヤの制御性をよくするために必須である。(2)ナノワイヤ列直下の寄生チャンネルの形成を抑止するために、平面部分にドーピングをおこなった。これによりリーク電流を抑止できた。

10nm未満CMOSデバイス実現のめどが立った

imecのロジック・デバイス集積担当ディレクターのDan Mocuta氏は「すでに業界で広く使われ技術が確立しているRMGプロセスを使い、直径8mの超微細ナノワイヤの積層が可能となり、サブ10nm技術ノードでデバイスを実用化するめどが立った。今回発表したデバイスのFinピッチは45nmだが、今後はピッチをさらに狭めて、ゲート・オール・アラウンド横型ナノワイヤCMOSデバイスの実現をめざす」と述べている。