産業技術総合研究所(産総研)は12月7日、半導体ICチップの偽造を防ぐ「ICの指紋」を低コスト、高信頼性、コンパクトに実現できる素子とそれを用いた回路技術を開発したと発表した。

同成果は、同研究所 ナノエレクトロニクス研究部門 ナノCMOS集積グループ 大内真一 主任研究員、柳永勛 上級主任研究員、松川貴 研究グループ長、エレクトロインフォマティクスグループ 堀洋平 主任研究員らによる研究グループによるもので、12月9日(現地時間)にワシントンD.C.にて行われる「国際電子デバイス会議(2015 International Electron Devices Meeting:IEDM)」にて発表される予定。

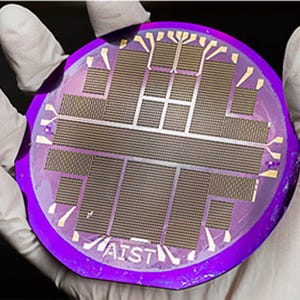

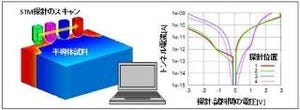

今回開発された「指紋」発生回路は、「指紋」となるICチップの固有番号を、「多結晶シリコンFinFET」で構成したSRAM回路によって発生するもの。このSRAM回路の起動時の初期値が0になるか1になるかは、製造時の素子性能のばらつきを反映して決まり、起動ごとに同じ値を示す。「指紋」発生回路には複数のSRAM回路が用いられ、SRAM回路数のビット数の番号を発生させることができる。個々のSRAM回路の初期値は製造工程でランダムに決まるため、発生した番号はICチップに固有の番号となる。固有番号ビット数を多くすれば同じ固有番号を持つ確率は小さくなるので、そのICチップを複製や偽造することはできない。

今回の研究では、多結晶シリコンFinFETを用いた「指紋」発生回路が、通常型FinFETの回路の3倍以上の安定性で固有番号を発生でき、高い確度でICチップを認証や同定できることが明らかになった。通常型FinFETの回路で128ビットの固有番号を同等の安定性で発生させる場合に比べ、多結晶シリコンFinFETの導入によって、少なくとも約15000トランジスタ分の回路を省略できると見積もられる。

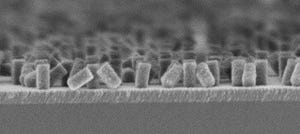

同技術で用いられる多結晶シリコンFinFETは、作製工程の初期段階にIC基板の一部に多結晶シリコン薄膜を堆積させた後、標準的なFinFET素子と同一の製造工程で同時に形成されるため、短工程で終了することができる。また、製造工程の条件が変化した場合でも発生される固有番号に偏りは生じないという。

同研究所は今後、製造工程の後工程で認証用回路のトランジスタを挿入する、デバイスレベル三次元構造への適用を検討していくとしている。