基調講演では簡単に性能面が(Cortex-A7と比較する形で)示された「Cortex-A35」だが、もう少し細かい話をご紹介したいと思う。

まず製品セグメントから。Photo01が各々の製品分け、という形になる。

実を言えばこの図は厳密にはCortex-A9とCortex-A53の間にARMv7-A(*)としてCortex-A12が入った形になる"はずだった"。ところがCortex-A12は発表こそされたものの、あまりニーズが無いということで、2014年10月にCortex-A17に統合される形になってしまい、この結果ARMv7-A(*)と書いた、32bitを超えるLPA(Large Physical Addressing)を利用できるHigh Efficency向けのARM v7-aベースのコアがなくなってしまった。実際に製品動向を見ると、Cortex-A15の動作周波数を落として使う、なんてケースがしばしば見られたのは、Cortex-A7とCortex-A15/17の間にかなりの性能ギャップがあったためである。

これもあってか、ARMv8-Aでは当初からCortex-A57とCortex-A53が比較的近い性能で登場しており、特にこのCortex-A53はかなり広く利用されたのだが、64bitの裾野が広がってきた(つまりOSやアプリケーションの64bitへの移行が進んだ)結果、性能はもう少し低くても良いから省電力で、かつ64bitにも対応できるプロセッサが望まれるようになった、というのは自然な成り行きであり、これに向けて投入されたのがCortex-A35という訳だ。

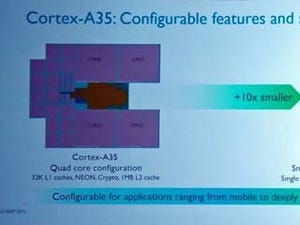

そのCortex-A35、絶対性能という意味ではかならずしも高くない。むしろ性能/消費電力比や性能/エリアサイズを高める事を優先したコアであり、このため基本はまるでCortex-A7を64bit化したような構成になっている(Photo02)。もっともこれに関しては「設計を見るとかなりCortex-A7に近いが、別にCortex-A7のパイプラインを持ってきたわけではなく、ScratchからCPUのパイプラインを設計するにあたり、ターゲットとした性能/回路規模/消費電力に見合う形で設計をした結果、似たような構成になった」(ARMのNandan Nayampally氏)という話であった。実際にはパイプラインの構造などはCortex-A7のものを参考にしつつ、ここにCortex-A53などでインプリメントされたARMv8-Aのエッセンスを統合した、というニュアンスの発言であった。

では具体的にどの改善されたかということでまずは電力比で言うと、当初のCortex-A7に比べて同一周波数で20%程度、28nmで最適化を行ったCortex-A7と比較しても10%程度の省電力化が実現したとする(Photo03)。またエリアサイズを25%縮小し、効率を25%改善したとする(Photo04)。

|

|

|

|

Photo03:28nmといっても色々あるのだが、ここでの比較は完全に同じ種類のプロセスということらしい。動作周波数がどのあたりか、は不明 |

Photo04:もっとも消費電力とか性能はもう動作周波数で大分変わってくるので、これは一概には言いにくいのだが |

さて、ここからもう少し内部の話を。Photo05が発表されたパイプライン構成である。パイプライン段数としてはALUの場合に8段とされている。ちょっとこれだと判りにくいので、比較対象のためにPhoto06にCortex-A7のパイプラインを示すが、おおむね各ステージは同程度の段数と思われる。

|

|

|

|

Photo05:Integer/Load-Storeの最後にあるETMはEmbedded Trace Macrocellの略で、これはARMのCoreSightと呼ばれるデバッグ用のものである。ETMの場合、プロセッサの動作をリアルタイムでトレース可能である。もちろんこれはオプション扱いである |

Photo06:こちらは2012年のARM Tech Symposia Tokyoにおける資料 |

ちなみにCortex-A7も一見するとDual Issuに見えるが、同時に実行できる命令は非常に限られており、実際にDual Issueで実行可能なのはALU/moveとbranch/call程度になっている。これは例えばGitHubに置かれたGCCのCortex-A7用のconfig-a7.mdを眺めると明白で、Dual issueで実行可能なのは

- ALU instruction with an immediate operand

- ALU instruction with register operands

の場合のみで、Callについてはolder instructionsや他の分岐命令との組み合わせはDual issueでは実行できないとしている。残念ながらCortex-A35用のConfigはまだ公開されていないが、インタビューで聞いた範囲ではほぼこの制約がそのままCortex-A35にも適用される感じであった。