ベルギーの独立系半導体・エレクトロニクス研究機関「imec」は、6月下旬にベルギーの首都Brusselsで年次研究計画発表イベント「imec Technology Forum2015」を開催し、そのなかで、半導体プロセス開発担当シニア・バイスプレジデントのAn Steegen氏(図1)が、「Internet of Things (IoT)のインフラストラクチャ」と題して、半導体デバイス・プロセスの今後の方向性について語った。

imecは、多数の人々に幸福をもたらすスマートリビング実現のためのIoTを研究所全体のテーマとして採りあげており、半導体はその実現のための鍵を握るスマートデバイス、微細化プロセスは、スマートデバイスを実現するための手段と位置付けている。「IoTのインフラ」と言う講演タイトルもこのような背景から付けられたものである。

An Steegen氏は、地元のルーベン・カトリック大学(KU Leucen)で博士号を取得後、imecに入社し、初期のプロセス開発に従事。その後、米国ニューヨーク州にあるIBMの研究施設へ転じて10年ほど先端半導体プロセス開発にあたった。2010年12月にimecに引き抜かれ、現在、imecの半導体プロセス研究開発の最高責任者として、7-5 nm CMOSプロセス およびポストCMOSプロセス開発チームを率いている。去る6月に京都で開催されたVLSIシンポジウムでも招待講演を行っており、次世代半導体プロセス開発の第一人者である。

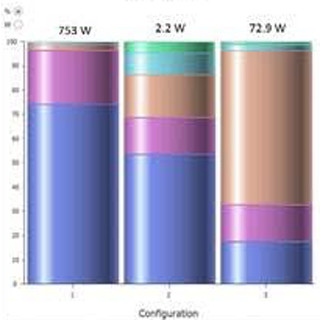

Steegen氏は、まず図2を示して、センサ端末から、ウォッチ、スマートフォン、PC、を経てサーバに至るIoTの主要構成要素には、消費電力、演算性能、I/Oバンド幅、記憶容量に関してそれぞれ異なった要求があり、それぞれの要求に応じた半導体デバイス開発が求められていることを説明した。そして今回は、すべてのモノをインターネットに結ぶIoTの要である、最も高性能を要求されるクラウドコンピュ―ティング用サーバ(図3)に焦点をしぼり、そのための半導体デバイスを実現するための今後のプロセス開発方向を紹介すると前置きして、話しを始めた。

半導体デバイスのパフォーマンス(単位消費電力当たり)を向上させるには、

- 回路パターンの微細化(scaling)

- デバイス構造および材料の変更

- ファンクションのスケーリング

の3通りの手法があるが、まず、デバイス構造の微細化の方向を紹介しよう。

図4に示すように、集積回路に搭載されたトランジスタ数は、ムーアの法則に従って2年で倍増してきており、最先端のMPUには50億個ものトランジスタが搭載されている。世代(技術ノード)が変わるごとに、回路パターンの寸法は伝統的に3割ずつ縮小し、面積は半減し続けている。

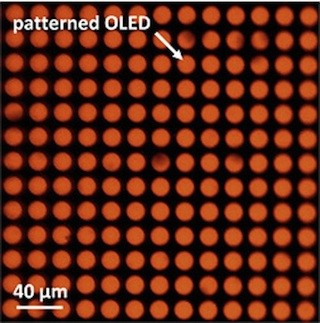

微細化は、リソグラフィの解像度を上げることにより実現できるため、露光装置の光源の波長は短波長側に移ってきており、65nm以降はArFレーザー光源(波長193nm)が使われている。20nm以降は、ダブルパターニングいう手法を併用している。露光を2回に分けて行うことにより、より微細なパターニングを行う方法だが、製造工数が倍増する。10nmからはトリプルパターニング、その先は4回以上のマルチパター二ングが必要となってしまい、製造コストが跳ね上がるので、量産には適用しにくい。もしもEUV(extreme ultra violet:極端紫外線)リソグラフィ(波長13.5nm)が使えれば、シングルパターニングが可能となるが、光源出力はじめいろいろな技術的課題を抱えており、未だ量産に使えるような段階にはない。

2015年の現時点では、数年後の7nmデバイスあたりから生産に導入される見込みである。さらに解像度を改善するにはN.A,(開口数)を大きくする必要があろう。これらの露光手段はきわめて高価であるので、それを補うためにDirected Self Assembly(DSA:誘導自己組織化)が近年急浮上してきた。光を用いずに高分子材料固有の性質を利用して、パターニングする手法で、大いに期待がかけられている。