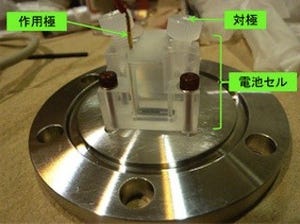

東京大学は12月15日、極低電圧での動作が可能な新しい構造のトンネル電界効果トランジスタを開発したと発表した。

同成果は、同大大学院 工学系研究科の高木信一教授らによるもの。詳細は、国際会議International Electron Device Meeting(IEDM)の「Technical Digest」に掲載された。

IT機器の消費エネルギーの増大は国際的にも重大な課題であり、従来のMOSトランジスタとは動作原理の異なる、極低消費電力で動作するデバイスの開発競争が激しくなっている。今回、研究グループは従来のMOSトランジスタとほぼ同等の素子構造で、Siに引っ張り応力を加えた歪みSiとGeのヘテロ界面からなる接合を用いる新しいトンネル電界効果トランジスタを開発した。同トランジスタでは、ゲート電圧のわずかな変化で極めて大きな電流変化を実現しており、素子のオン状態とオフ状態の電流比を107以上と、世界最高クラスの値まで高めることに成功している。

同素子を用いることで、現行では0.9Vのトランジスタの電源電圧を0.3V以下まで低下させることができるため、IT機器の省電力化をもたらし、バッテリが不要な集積回路など、新しい応用を可能にすることが期待されるとコメントしている。