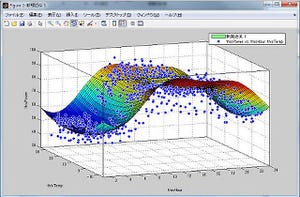

AlteraとMathWorksは11月5日(米国時間)、MathWorksのMATLAB/Simulink Release 2014bに、AlteraのARMベースSoC FPGA向けに最適化されたモデルベースのデザイン・ワークフローを提供することを発表した。

これにより、プログラマはSoC FPGAに統合されたFPGAとARMプロセッサの両方をターゲットにしたアルゴリズムをシミュレート、プロトタイピング、検証、および実装することができるようになるほか、FPGA、プロセッサ・システム、およびソフトウェア・ドライバとのインタフェースを自動的に生成することが可能になる。

具体的にはHDL CoderとEmbedded Coderの2つのコード生成製品を、単一の開発環境にて活用することで、SoCのプログラマブル・ロジック部分とARMベースのハード・プロセッサ・システム上で動作するC/C++コードの双方を生成することが可能になり、結果として開発期間の短縮を実現することができるようになるという。

また、Release 2014bには、Cyclone V SoC開発ボードの自動プログラミングを含む、アルテラの低コストCyclone V SoC向けの自動化サポートも含まれているという。